I made my own board using TMS320C6657.

My developing envirement is CCS5.5 IDE with XDS2xx USB Emulator.

My board's power sequencing is IO-before-Core just the same as the EVM6657

with device configuration being no-boot mode and using evmc6657l.gel file of EVM6657 to initialize DSP.

After power on and my IDE's being connected to DSP using emulator through JTAG port,the .gel file is executed normally.

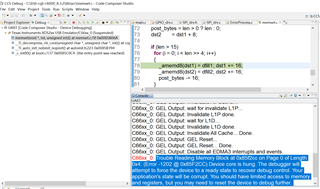

But before going to my main() function, the following information occured:

C66xx_0:

Trouble Reading Memory Block at 0x85f1ac on Page 0 of Length 0x4:

(Error -1202 @ 0x85F1AC) Device core is hung.

The debugger will attempt to force the device to a ready state to recover debug control.

Your application's state will be corrupt. You should have limited access to memory and registers,

but you may need to reset the device to debug further. (Emulation package 5.1.232.0)

This was the IDE UI's snapshot:

This occured every time I power up my board .

Could any experienced engineer give me some solving methods or possible clues for this malfunction ?

Thank you very much!!