Hi Ti,

Do you have any further information of "PADCFG_CTRL0_CFG0" of AM6548?

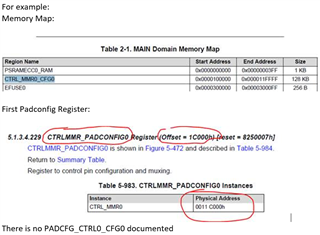

I can find it in AM64 TRM but not in AM65. Below is the screen shot from AM64.

Or is there any other document related to this?

Eric

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi Ti,

Do you have any further information of "PADCFG_CTRL0_CFG0" of AM6548?

I can find it in AM64 TRM but not in AM65. Below is the screen shot from AM64.

Or is there any other document related to this?

Eric

Hello Eric,

Thank you for the query.

Looks like there are some naming convention changes.

Could you please review the below sections in the device specific TRM and let me know if this is in line with what you are looking for.

AM65

5.1.3.4 CTRL_MMR0 Registers

AM64

5.1.1.4 PADCFG_CTRL0_CFG0 Registers

Regards,

Sreenivasa

I got a patch of AM64 as below and I want to see if AM65 can use this or not.

+static void wwctrl_mmr_unlock(void)

+{

+ /* Unlock all PADCFG_MMR1 module registers */

+ mmr_unlock(PADCFG_MMR1_BASE, 1);

+

+ mmr_unlock(CTRL_MMR0_BASE, 0);

+ mmr_unlock(CTRL_MMR0_BASE, 1);

+ mmr_unlock(CTRL_MMR0_BASE, 2);

+ mmr_unlock(CTRL_MMR0_BASE, 3);

+ mmr_unlock(CTRL_MMR0_BASE, 5);

+ mmr_unlock(CTRL_MMR0_BASE, 6);

+}

It needs the address of PADCFG_MMR1_BASE and CTRL_MMR0_BASE.

They are 0xf0000 and 0x43000000 in AM64.

In AM64 TRM, 0x43000000 is CTRL_MMR0_CFG0. And 0xf0000 is PADCFG_CTRL0_CFG0.

However, I have no idea how they mapping to AM65.

In AM65, I only found CTRL_MMR0_CFG0 and is 0x0000100000. It's different from AM64. I'm not sure if it's correct.

And I also cannot find PADCFG_CTRL0_CFG0 in AM65.

Could you help this?

Thanks.

Eric

Hello Eric,

Thank you for the inputs.

Let me check internally.

Would it be possible for you to share some details on the development environment you are using.

Regards,

Sreenivasa

I'm still using LINUX RT SDK7, we are based on this.

And actually, we are trying to fix issue like this one, section 3.2.2.7.5 in the below link.

Eric

Hello Eric,

Thank you for the inputs.

I am checking internally.

Regards,

Sreenivasa

Hello Eric,

Thank you for following.

I am checking internally and will update you.

Regards,

Sreenivasa

Hello Eric,

Thank you for following.

Please check below inputs received and let me know if this helps

In AM65, the padconfig registers are split between the Main and WKUP domain MMRs

From the TRM:

Main domain base: CTRL_MMR0_CFG0 - 00100000h

First padconfig register: CTRLMMR_PADCONFIG0 - 1C000h offset, 0011C000h physical

Regards,

Sreenivasa