Other Parts Discussed in Thread: UNIFLASH, , DP83848K

Hello,

I work on the same projekt mentioned in AM4377: QSPI-Flash for AM4377 and we still have the problem that sometimes the board doesn't boot.

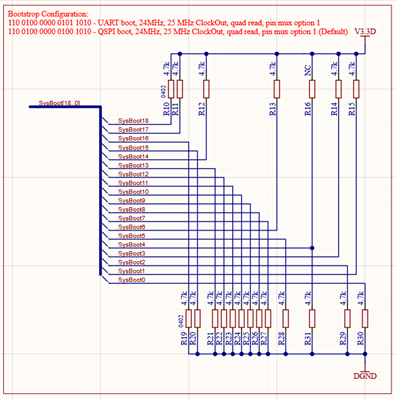

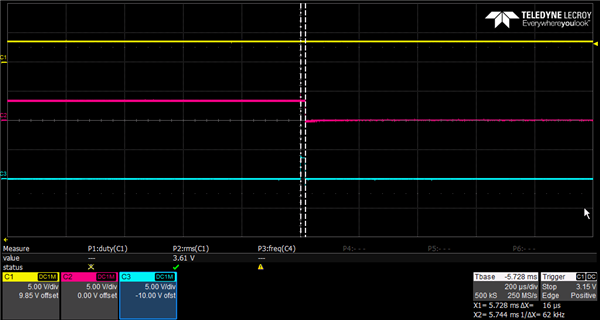

I have measured DCLK and nCS of the QSPI when the boot process fails and the communication doesn't even start even though the SYSBOOT configuration being in QSPI (110'0100'0000'0100'1010) mode.

Is there any way to make sure we are in the correct boot mode?

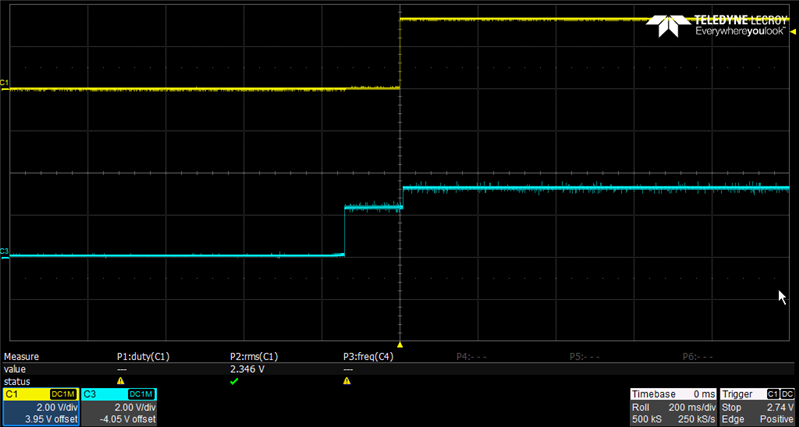

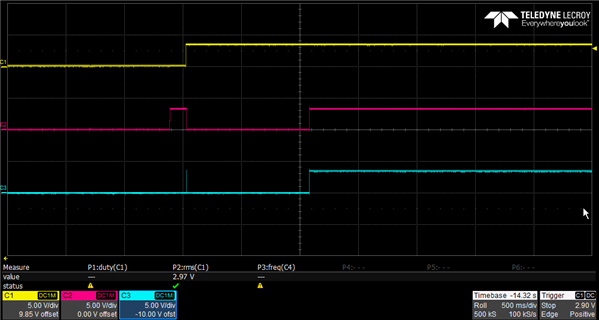

Maybe it's a hardware problem, because some boards work perfectly, while others get the error about every other time. I was able to reproduce the fault with a "bad" board consistently with power cycling the device when it's on with about 0.5s off time. If the device is turned off for longer than about a second it boots without any problems. In both cases the power sequencing is the same. I think this is an argument against a hardware fault.

A maybe related problem i discovered:

The following problems are just happening with the "bad" boards which are around 20%. With the others the programming with the UniFlash is successful.

When programming the flash memory via the UniFlash CLI, after loading the .out file with the USB560v2 System Trace over JTAG, there is no output of "C" on the COM-port despite the return value beeing succesful.

CMD line instruction:

.\dslite.bat --mode load --config=PATH\TargetConfig\sqpAM437x.ccxml -f PATH\ProgFiles\uart_sqpAM437x_flash_programmer.out -n 1

Output:

> "C:\TI\uniflash_8.1.1\deskdb\content\TICloudAgent\win\ccs_base\DebugServer\bin\DSLite" load --config=PATH\TargetConfig\sqpAM437x.ccxml -f PATH\ProgFiles\uart_sqpAM437x_flash_programmer.out -n 1

For more details and examples, please refer to the UniFlash Quick Start guide.

DSLite version 12.2.0.2919

Configuring Debugger (may take a few minutes on first launch)...

Initializing Register Database...

Initializing: IcePick_D_0

Loaded FPGA Image: C:\TI\uniflash_8.1.1\deskdb\content\TICloudAgent\win\ccs_base\common\uscif\dtc_top.jbc

Executing Startup Scripts: IcePick_D_0

Initializing: CS_DAP_M3

Executing Startup Scripts: CS_DAP_M3

Initializing: M3_wakeupSS_1

Executing Startup Scripts: M3_wakeupSS_1

Initializing: CS_DAP_DebugSS

Executing Startup Scripts: CS_DAP_DebugSS

Initializing: CortexA9

Executing Startup Scripts: CortexA9

Initializing: CSSTM_0

Executing Startup Scripts: CSSTM_0

Initializing: CSETB_0

Executing Startup Scripts: CSETB_0

Initializing: PRU_ICSS1_PRU0

Executing Startup Scripts: PRU_ICSS1_PRU0

Initializing: PRU_ICSS1_PRU1

Executing Startup Scripts: PRU_ICSS1_PRU1

Initializing: PRU_ICSS0_PRU0

Executing Startup Scripts: PRU_ICSS0_PRU0

Initializing: PRU_ICSS0_PRU1

Executing Startup Scripts: PRU_ICSS0_PRU1

Connecting...

GEL: CortexA9: Output: **** AM437x SQP Initialization is in progress ..........

GEL: CortexA9: Output: **** Device Type: GP

GEL: CortexA9: GEL Output: System input clock is 24MHz

GEL: CortexA9: GEL Output: **** AM43xx NITRO (1000MHz) with CLKIN=24MHz is in progress .........

GEL: CortexA9: GEL Output: **** Going to Bypass...

GEL: CortexA9: GEL Output: **** Bypassed, changing values...

GEL: CortexA9: Output: **** Locking PLL

GEL: CortexA9: GEL Output: **** MPU PLL locked

GEL: CortexA9: GEL Output: **** Core Bypassed

GEL: CortexA9: GEL Output: **** Now locking Core...

GEL: CortexA9: GEL Output: **** Core locked

GEL: CortexA9: GEL Output: **** Calculated PER SD Divisor=4

GEL: CortexA9: GEL Output: **** PER DPLL Bypassed

GEL: CortexA9: GEL Output: **** PER DPLL Locked

GEL: CortexA9: GEL Output: **** Calculated EXTDEV SD Divisor=2

GEL: CortexA9: GEL Output: **** EXTDEV DPLL Bypassed

GEL: CortexA9: GEL Output: **** EXTDEV DPLL Locked

GEL: CortexA9: GEL Output: **** DISP PLL Config is in progress ..........

GEL: CortexA9: GEL Output: **** DISP PLL Locked

GEL: CortexA9: GEL Output: **** DDR DPLL Bypassed

GEL: CortexA9: GEL Output: **** DDR DPLL Locked

GEL: CortexA9: GEL Output: **** Setting DDR3 = 400MHz

GEL: CortexA9: GEL Output: **** AM43xx NITRO configuration is done .........

GEL: CortexA9: GEL Output: Starting DDR3 configuration...

GEL: CortexA9: Output: EMIF PRCM is in progress .......

GEL: CortexA9: Output: EMIF PRCM Done

GEL: CortexA9: GEL Output: EMIF CLK enabled...

GEL: CortexA9: GEL Output: Waiting for VTP Ready .......

GEL: CortexA9: GEL Output: VTP is Ready!

GEL: CortexA9: GEL Output: VTP controller enabled

GEL: CortexA9: GEL Output: Checking if DLL is ready...

GEL: CortexA9: GEL Output: DLL is ready

GEL: CortexA9: GEL Output: Configuring DDR IOs and Control Module registers...

GEL: CortexA9: GEL Output: Configuration of Control Module registers complete

GEL: CortexA9: GEL Output: Setting up DDR3 H/W leveling configuration...

GEL: CortexA9: GEL Output: Starting EMIF controller configuration...

GEL: CortexA9: GEL Output: EMIF Config for SQP

GEL: CortexA9: GEL Output:

DDR3 Hardware leveling complete... Outputing all the leveling results !!!

GEL: CortexA9: GEL Output: PHY_STATUS_12=0x07000099

GEL: CortexA9: GEL Output: PHY_STATUS_13=0x070000A0

GEL: CortexA9: GEL Output: PHY_STATUS_14=0x070000B4

GEL: CortexA9: GEL Output: PHY_STATUS_15=0x070000AD

GEL: CortexA9: GEL Output: PHY_STATUS_16=0x00000000

GEL: CortexA9: GEL Output: PHY_STATUS_7 =0x00000046

GEL: CortexA9: GEL Output: PHY_STATUS_8 =0x00000044

GEL: CortexA9: GEL Output: PHY_STATUS_9 =0x00000046

GEL: CortexA9: GEL Output: PHY_STATUS_10=0x00000044

GEL: CortexA9: GEL Output: PHY_STATUS_11=0x00000000

GEL: CortexA9: GEL Output: PHY_STATUS_17=0x012700D1

GEL: CortexA9: GEL Output: PHY_STATUS_18=0x000000CD

GEL: CortexA9: GEL Output: PHY_STATUS_19=0x019300E0

GEL: CortexA9: GEL Output: PHY_STATUS_20=0x010300DF

GEL: CortexA9: GEL Output: PHY_STATUS_21=0x00000000

GEL: CortexA9: GEL Output: PHY_STATUS_22=0x00E70091

GEL: CortexA9: GEL Output: PHY_STATUS_23=0x03C0008D

GEL: CortexA9: GEL Output: PHY_STATUS_24=0x015300A0

GEL: CortexA9: GEL Output: PHY_STATUS_25=0x00C3009F

GEL: CortexA9: GEL Output: PHY_STATUS_26=0x00000000

GEL: CortexA9: GEL Output:

DDR3 configuration is complete!!!

GEL: CortexA9: GEL Output: Turning on EDMA...

GEL: CortexA9: GEL Output: EDMA is turned on...

GEL: CortexA9: Output: **** AM437x IDK EVM Initialization is Done ******************

GEL: CortexA9: Output: **** PRU-ICSS PRCM Enable Step 1 is in progress ****

GEL: CortexA9: Output: **** PRU-ICSS PRCM Enable Step 1 is Done ****

GEL: CortexA9: Output: **** PRU-ICSS PRCM Enable Step 2 is in progress ****

GEL: CortexA9: Output: **** PRU-ICSS PRCM Enable Step 2 is Done ****

Fill Memory

Verifying 0x54410000

Filling 0x54417FF0: 99%

Verifying 0x54417FF0: 99%

Filling 0x54418000: 100%

Loading Program: PATH\ProgFiles\uart_sqpAM437x_flash_programmer.out

Preparing ...

PT_LOAD[0]: 0 of 40084 at 0x40300000

PT_LOAD[0]: 32752 of 40084 at 0x40300000: 81%

Finished: 81%

Setting PC to entry point.: 81%

Running...

Success

When loading the .out-file with the Code Composer Studio (10.4.0.00006) the "C" output on the COM-port is there but most of the times the process fails at 8% when trying to flash the image.

When this happens the QSPI-communication also doesn't start. When i try it this way the loading is succesful 1 out of 10 times.

CMD line instruction:

C:\TI\uniflash_8.1.1>dslite.bat --mode processors -c COM6 -f PATH\ProgFiles\bootloader_boot_qspi_a9host_release.bin -d 2 -o 0

Output:

Executing the following command: > C:\TI\uniflash_8.1.1\processors\ProcessorSDKSerialFlash.exe -c COM6 -f PATH\ProgFiles\bootloader_boot_qspi_a9host_release.bin -d 2 -o 0 For more details and examples, please refer to the UniFlash Quick Start guide. The file extension is .bin ---------------------------------------------------------------------------- ProcessorSDKSerialFlash CLI Tool Copyright (C) 2017-2022 Texas Instruments Incorporated - http://www.ti.com/ Version 1.7.0.0 ---------------------------------------------------------------------------- Transferring the Image to Flash Programmer.. Transferring Header Information.. Header Transfer Complete! Flashing Image of size 37768 bytes 8% complete Flash Programming Failed!!

When trying to delete the flash memory there is also no communication between flash and am4377 even tough it says Flash Erase Success!

CMD line instruction:

C:\TI\uniflash_8.1.1>dslite.bat --mode processors -c COM6 -d 2 -e 0x200000

Output:

Executing the following command: > C:\TI\uniflash_8.1.1\processors\ProcessorSDKSerialFlash.exe -c COM6 -d 2 -e 0x200000 For more details and examples, please refer to the UniFlash Quick Start guide. ---------------------------------------------------------------------------- ProcessorSDKSerialFlash CLI Tool Copyright (C) 2017-2022 Texas Instruments Incorporated - http://www.ti.com/ Version 1.7.0.0 ---------------------------------------------------------------------------- Erasing Flash.... Transferring Header information.. Header Transfer Complete!! Flash Erase Success!

In the Quicik start guide it says with %errorlevel% it's possible to check if the previous operation passed. In my case this is true for the "dslite.bat --mode load ..." command but the "dslite.bat --mode processors ..." instruction always returns 1 even if everything loads succesful (bootloader and .bin file).

Is this a bug of the batch file or is it sure that something is wrong? And is there any other way to ensure the process is succesful/failed?

Do you have any suggestions on how to proceed?

Regards, Timo