- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

On the AM62 SK DTS there is the following:

AM62X_IOPAD(0x11c, PIN_INPUT, 0) /* (#N/A) MMC2_CLKB */

This is not present when generating the .dtsi using the sysconfig tool and it’s writing to a non documented registers.

Question was asked at another thread in the past with no answer - https://e2e.ti.com/support/processors-group/processors/f/processors-forum/1126003/am625-mmc2_clkb-in-k3-am625-sk-dts

Do we need it to use the MMC2 interface as SDIO?

If yes:

what is this doing ?

where is this documented?

Hi,

I am working internally to understand this MMC2_CLKB pin and how it comes to the kernel DTS. I will get back to you once I have an update.

Hi,

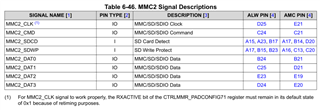

I haven't received a response from our dev team yet, but I found the following note in the Datasheet. I believe this is the reason of this pinmux setting. The PADCONFIG71 register offset is 0x11c.

Do you have a feedback as yet?

I agree, this is very likely this PADCONFIG71 mentioned on the datasheet section you pasted here.

However if it must remains at default state why writing it?

Moreover the value written in the TI DTS file is not the default, different bits are set. What is wrong? The datasheet or the DTS?

Hi,

Do you have a feedback as yet?

Not yet.

However if it must remains at default state why writing it?

In many case, the kernel device tree still wants to specifically set the default state, to decouple any configuration state left from U-Boot.

Moreover the value written in the TI DTS file is not the default, different bits are set. What is wrong? The datasheet or the DTS?

Yes, I noticed the Datasheet states the RXACTIVE bit default is 0x1, while the TRM register description section says RXACTIVE bit default is 0x0. I have filed a ticket to our documentation team to check this inconsistency.

The team is still working on clarifying the default value of the register and to update the documentation accordingly. But regardless, the RXACTIVE bit should be set to 1 as what the DTS pinmux does.

Any update? please do not forget about this question about the inconsistency between mmc2 and mmc0/mmc1.

Hi Isee,

My apologies for missed updating this thread.

The RXACTIVE bit in the PADCONFIG register for mmc0/mmc1 by default is 1, but it is default to 0 for mmc2. So the Linux device tree only sets it to 1 in mmc2 node, but not in mmc0/mmc1 nodes.