Part Number: AMIC110

Other Parts Discussed in Thread: TLK106, , TLK105

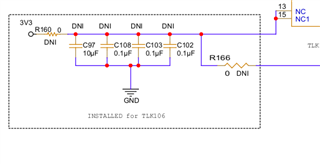

Hi all. I have a custom board modeled after the TMDX110 ICE board that I am using for an EtherCAT application, except that I used TLK106 parts for the PHYs, since the DP83822s are unavailable.

I have discovered that my PHY2 port (the one that is connected to J7 on the ICE board, and is supposed to be the upstream port) isn't working. PHY1 seems to work fine, and my system works with that port, although since it is the downstream port, it throws an EtherCAT warning. The PHY2 that isn't working does show a link light when I plug it in. But it doesn't talk to the master.

I've checked my schematics against the AMIC110 ICE EVM Rev 1.1 schematics for the PHY connections to the micro, and with the exception of the TLK106 modifications, it all matches up, except I have the MDIO address on PHY2 set to 5 instead of 13 as is on the ICE. The software on the AMIC110 talks to the PHY OK once I changed the address to 5 from 13. Could that be a problem for the PRU firmware?

I noticed that there are separate drivers/setup software for the TLK parts in the board support code base. I thought maybe I needed to play with that, but since PHY1 works, I thought it wasn't a problem. Could it be a PHY setup problem or a strap problem?

I'm wondering how to go about debugging this. I saw from another e2e post that the Ethercat PRU firmware source isn't available, so I guess I'm reduced to probing the AMIC110 code. I have some spare GPIO pins I could use to output to a logic analyser or scope.

John