Other Parts Discussed in Thread: TDA4VL,

Hi, TI expert

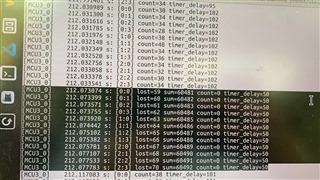

We used 12 DMA channels in mcu3-0, and after modifying "rm cfg. c" to allocate DMA resources, the 12 channel DMAs worked normally. However, when using timerP at the same time in mcu3-0, many times the DMAs caught missing or unable to catch data. If timerP is not applicable, this situation will not exist.

Version information: sdk8.02 Linux&rtos.

Please assist in the investigation, thank you~!