Other Parts Discussed in Thread: TDA4VM

Dear TI experts,

we got a problem when boot the tda4ve board, the ddr init failed!

we used samsung ddr K4FBE3D4HB-KHCL, we used the SPRACU8B_Jacinto7_DDRSS_RegConfigTool.xlsb tool to change the parameters, if we set the ddr rate to 3733, the ddr init failed,

the uboot log like below:

U-Boot SPL 2021.01-dirty (Jul 20 2023 - 16:08:43 +0800)

ti_sci system-controller@44083000: Message not acknowledgedti_sci system-controller@44083000: Message no)

EEPROM not available at 0x50, trying to read at 0x51

Reading on-board EEPROM at 0x51 failed 1

k3_ddrss_probe(dev=41c6771c) name memorycontroller@2990000

--->>> k3_lpddr4_read_ddr_type: 203 ... 0x000b<<<---

--->>> k3_ddrss_init_freq: 283 ... ddr_freq0:27500000<<<---

--->>> k3_lpddr4_start: 551 ... <<<---

--->>> LPDDR4 Initialization is in progress ... <<<---

--->>> k3_lpddr4_read_ddr_type: 203 ... 0x000b<<<---

--->>> k3_lpddr4_freq_update: 245 ...<<<---

--->>> lpddr4_startsequencecontroller: 114 ...<<<---

when we config the data rate to 1200 , the board boot successfully

but we need to change the below register in file (k3-j721s2-ddr-evm-lp4-1200.dtsi) mannually

DDRSS0_PHY_1303_DATA 0x00000064 -> 0x0000FFFF

DDRSS1_PHY_1303_DATA 0x00000064 -> 0x0000FFFF

we also used the tda4vm_lp4_debug.out to test the ddr ,we attach the log file (ccs-ddr-3733-072001.txt) below

Can you help us to figure out how can we increase the DDR rate,

SDK : ti-processor-sdk-linux-j721s2-evm-08_06_01_02

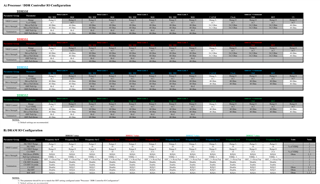

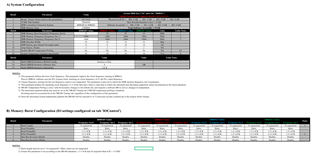

SPRACU8B_Jacinto7_DDRSS_RegConfigTool parameters:

[MCU_Cortex_R5_0] Training Results; Frequency 0; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x2b ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 680 CA Bit 1 delay: 680 CA Bit 2 delay: 680 CA Bit 3 delay: 680 CA Bit 4 delay: 680 CA Bit 5 delay: 680 Write Leveling: DQ Lane 0 WRDQS: 0x28 DQ Lane 1 WRDQS: 0x1ec DQ Lane 2 WRDQS: 0x1e8 DQ Lane 3 WRDQS: 0x3c DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 109 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 160 read_delay_rise, dq0 : 160 read_delay_fall, dq1 : 160 read_delay_rise, dq1 : 160 read_delay_fall, dq2 : 160 read_delay_rise, dq2 : 160 read_delay_fall, dq3 : 160 read_delay_rise, dq3 : 160 read_delay_fall, dq4 : 160 read_delay_rise, dq4 : 160 read_delay_fall, dq5 : 160 read_delay_rise, dq5 : 160 read_delay_fall, dq6 : 160 read_delay_rise, dq6 : 160 read_delay_fall, dq7 : 160 read_delay_rise, dq7 : 160 read_delay_fall, dq8 : 160 read_delay_rise, dq8 : 160 read_delay_fall, dq9 : 160 read_delay_rise, dq9 : 160 read_delay_fall, dq10 : 160 read_delay_rise, dq10 : 160 read_delay_fall, dq11 : 160 read_delay_rise, dq11 : 160 read_delay_fall, dq12 : 160 read_delay_rise, dq12 : 160 read_delay_fall, dq13 : 160 read_delay_rise, dq13 : 160 read_delay_fall, dq14 : 160 read_delay_rise, dq14 : 160 read_delay_fall, dq15 : 160 read_delay_rise, dq15 : 160 read_delay_fall, dq16 : 160 read_delay_rise, dq16 : 160 read_delay_fall, dq17 : 160 read_delay_rise, dq17 : 160 read_delay_fall, dq18 : 160 read_delay_rise, dq18 : 160 read_delay_fall, dq19 : 160 read_delay_rise, dq19 : 160 read_delay_fall, dq20 : 160 read_delay_rise, dq20 : 160 read_delay_fall, dq21 : 160 read_delay_rise, dq21 : 160 read_delay_fall, dq22 : 160 read_delay_rise, dq22 : 160 read_delay_fall, dq23 : 160 read_delay_rise, dq23 : 160 read_delay_fall, dq24 : 160 read_delay_rise, dq24 : 160 read_delay_fall, dq25 : 160 read_delay_rise, dq25 : 160 read_delay_fall, dq26 : 160 read_delay_rise, dq26 : 160 read_delay_fall, dq27 : 160 read_delay_rise, dq27 : 160 read_delay_fall, dq28 : 160 read_delay_rise, dq28 : 160 read_delay_fall, dq29 : 160 read_delay_rise, dq29 : 160 read_delay_fall, dq30 : 160 read_delay_rise, dq30 : 160 read_delay_fall, dq31 : 160 read_delay_rise, dq31 : 160 Write DQ Training: write_delay, dq0 : 640 write_delay, dq1 : 640 write_delay, dq2 : 640 write_delay, dq3 : 640 write_delay, dq4 : 640 write_delay, dq5 : 640 write_delay, dq6 : 640 write_delay, dq7 : 640 write_delay, dq8 : 640 write_delay, dq9 : 640 write_delay, dq10 : 640 write_delay, dq11 : 640 write_delay, dq12 : 640 write_delay, dq13 : 640 write_delay, dq14 : 640 write_delay, dq15 : 640 write_delay, dq16 : 640 write_delay, dq17 : 640 write_delay, dq18 : 640 write_delay, dq19 : 640 write_delay, dq20 : 640 write_delay, dq21 : 640 write_delay, dq22 : 640 write_delay, dq23 : 640 write_delay, dq24 : 640 write_delay, dq25 : 640 write_delay, dq26 : 640 write_delay, dq27 : 640 write_delay, dq28 : 640 write_delay, dq29 : 640 write_delay, dq30 : 640 write_delay, dq31 : 640 Calibration Registers: CAL_OBS_0: 0x008136d6 CAL_OBS_2: 0x00813793 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00136d64 CAL_OBS_5: 0x00137938 CAL_OBS_6: 0x00f36d6f CAL_OBS_7: 0x03f3793f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0350 phy_grp1_slave_delay_0: 0x0350 phy_grp2_slave_delay_0: 0x0300 phy_grp3_slave_delay_0: 0x0338 phy_grp0_slave_delay_1: 0x0300 phy_grp1_slave_delay_1: 0x0350 phy_grp2_slave_delay_1: 0x0300 phy_grp3_slave_delay_1: 0x0300 phy_top_train_calib_error_info: 0x00000001 Training Results; Frequency 0; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x2b ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 680 CA Bit 1 delay: 680 CA Bit 2 delay: 680 CA Bit 3 delay: 680 CA Bit 4 delay: 680 CA Bit 5 delay: 680 Write Leveling: DQ Lane 0 WRDQS: 0x0 DQ Lane 1 WRDQS: 0x0 DQ Lane 2 WRDQS: 0x0 DQ Lane 3 WRDQS: 0x0 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 109 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 160 read_delay_rise, dq0 : 160 read_delay_fall, dq1 : 160 read_delay_rise, dq1 : 160 read_delay_fall, dq2 : 160 read_delay_rise, dq2 : 160 read_delay_fall, dq3 : 160 read_delay_rise, dq3 : 160 read_delay_fall, dq4 : 160 read_delay_rise, dq4 : 160 read_delay_fall, dq5 : 160 read_delay_rise, dq5 : 160 read_delay_fall, dq6 : 160 read_delay_rise, dq6 : 160 read_delay_fall, dq7 : 160 read_delay_rise, dq7 : 160 read_delay_fall, dq8 : 160 read_delay_rise, dq8 : 160 read_delay_fall, dq9 : 160 read_delay_rise, dq9 : 160 read_delay_fall, dq10 : 160 read_delay_rise, dq10 : 160 read_delay_fall, dq11 : 160 read_delay_rise, dq11 : 160 read_delay_fall, dq12 : 160 read_delay_rise, dq12 : 160 read_delay_fall, dq13 : 160 read_delay_rise, dq13 : 160 read_delay_fall, dq14 : 160 read_delay_rise, dq14 : 160 read_delay_fall, dq15 : 160 read_delay_rise, dq15 : 160 read_delay_fall, dq16 : 160 read_delay_rise, dq16 : 160 read_delay_fall, dq17 : 160 read_delay_rise, dq17 : 160 read_delay_fall, dq18 : 160 read_delay_rise, dq18 : 160 read_delay_fall, dq19 : 160 read_delay_rise, dq19 : 160 read_delay_fall, dq20 : 160 read_delay_rise, dq20 : 160 read_delay_fall, dq21 : 160 read_delay_rise, dq21 : 160 read_delay_fall, dq22 : 160 read_delay_rise, dq22 : 160 read_delay_fall, dq23 : 160 read_delay_rise, dq23 : 160 read_delay_fall, dq24 : 160 read_delay_rise, dq24 : 160 read_delay_fall, dq25 : 160 read_delay_rise, dq25 : 160 read_delay_fall, dq26 : 160 read_delay_rise, dq26 : 160 read_delay_fall, dq27 : 160 read_delay_rise, dq27 : 160 read_delay_fall, dq28 : 160 read_delay_rise, dq28 : 160 read_delay_fall, dq29 : 160 read_delay_rise, dq29 : 160 read_delay_fall, dq30 : 160 read_delay_rise, dq30 : 160 read_delay_fall, dq31 : 160 read_delay_rise, dq31 : 160 Write DQ Training: write_delay, dq0 : 640 write_delay, dq1 : 640 write_delay, dq2 : 640 write_delay, dq3 : 640 write_delay, dq4 : 640 write_delay, dq5 : 640 write_delay, dq6 : 640 write_delay, dq7 : 640 write_delay, dq8 : 640 write_delay, dq9 : 640 write_delay, dq10 : 640 write_delay, dq11 : 640 write_delay, dq12 : 640 write_delay, dq13 : 640 write_delay, dq14 : 640 write_delay, dq15 : 640 write_delay, dq16 : 640 write_delay, dq17 : 640 write_delay, dq18 : 640 write_delay, dq19 : 640 write_delay, dq20 : 640 write_delay, dq21 : 640 write_delay, dq22 : 640 write_delay, dq23 : 640 write_delay, dq24 : 640 write_delay, dq25 : 640 write_delay, dq26 : 640 write_delay, dq27 : 640 write_delay, dq28 : 640 write_delay, dq29 : 640 write_delay, dq30 : 640 write_delay, dq31 : 640 Calibration Registers: CAL_OBS_0: 0x008136d6 CAL_OBS_2: 0x00813793 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00136d64 CAL_OBS_5: 0x00137938 CAL_OBS_6: 0x00f36d6f CAL_OBS_7: 0x03f3793f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0350 phy_grp1_slave_delay_0: 0x0350 phy_grp2_slave_delay_0: 0x0300 phy_grp3_slave_delay_0: 0x0338 phy_grp0_slave_delay_1: 0x0300 phy_grp1_slave_delay_1: 0x0350 phy_grp2_slave_delay_1: 0x0300 phy_grp3_slave_delay_1: 0x0300 phy_top_train_calib_error_info: 0x00000001 Training Results; Frequency 1; CS 0 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x2b ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 300 CA Bit 1 delay: 300 CA Bit 2 delay: 300 CA Bit 3 delay: 300 CA Bit 4 delay: 300 CA Bit 5 delay: 300 Write Leveling: DQ Lane 0 WRDQS: 0x0 DQ Lane 1 WRDQS: 0x0 DQ Lane 2 WRDQS: 0x0 DQ Lane 3 WRDQS: 0x0 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 109 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 160 read_delay_rise, dq0 : 160 read_delay_fall, dq1 : 160 read_delay_rise, dq1 : 160 read_delay_fall, dq2 : 160 read_delay_rise, dq2 : 160 read_delay_fall, dq3 : 160 read_delay_rise, dq3 : 160 read_delay_fall, dq4 : 160 read_delay_rise, dq4 : 160 read_delay_fall, dq5 : 160 read_delay_rise, dq5 : 160 read_delay_fall, dq6 : 160 read_delay_rise, dq6 : 160 read_delay_fall, dq7 : 160 read_delay_rise, dq7 : 160 read_delay_fall, dq8 : 160 read_delay_rise, dq8 : 160 read_delay_fall, dq9 : 160 read_delay_rise, dq9 : 160 read_delay_fall, dq10 : 160 read_delay_rise, dq10 : 160 read_delay_fall, dq11 : 160 read_delay_rise, dq11 : 160 read_delay_fall, dq12 : 160 read_delay_rise, dq12 : 160 read_delay_fall, dq13 : 160 read_delay_rise, dq13 : 160 read_delay_fall, dq14 : 160 read_delay_rise, dq14 : 160 read_delay_fall, dq15 : 160 read_delay_rise, dq15 : 160 read_delay_fall, dq16 : 160 read_delay_rise, dq16 : 160 read_delay_fall, dq17 : 160 read_delay_rise, dq17 : 160 read_delay_fall, dq18 : 160 read_delay_rise, dq18 : 160 read_delay_fall, dq19 : 160 read_delay_rise, dq19 : 160 read_delay_fall, dq20 : 160 read_delay_rise, dq20 : 160 read_delay_fall, dq21 : 160 read_delay_rise, dq21 : 160 read_delay_fall, dq22 : 160 read_delay_rise, dq22 : 160 read_delay_fall, dq23 : 160 read_delay_rise, dq23 : 160 read_delay_fall, dq24 : 160 read_delay_rise, dq24 : 160 read_delay_fall, dq25 : 160 read_delay_rise, dq25 : 160 read_delay_fall, dq26 : 160 read_delay_rise, dq26 : 160 read_delay_fall, dq27 : 160 read_delay_rise, dq27 : 160 read_delay_fall, dq28 : 160 read_delay_rise, dq28 : 160 read_delay_fall, dq29 : 160 read_delay_rise, dq29 : 160 read_delay_fall, dq30 : 160 read_delay_rise, dq30 : 160 read_delay_fall, dq31 : 160 read_delay_rise, dq31 : 160 Write DQ Training: write_delay, dq0 : 640 write_delay, dq1 : 640 write_delay, dq2 : 640 write_delay, dq3 : 640 write_delay, dq4 : 640 write_delay, dq5 : 640 write_delay, dq6 : 640 write_delay, dq7 : 640 write_delay, dq8 : 640 write_delay, dq9 : 640 write_delay, dq10 : 640 write_delay, dq11 : 640 write_delay, dq12 : 640 write_delay, dq13 : 640 write_delay, dq14 : 640 write_delay, dq15 : 640 write_delay, dq16 : 640 write_delay, dq17 : 640 write_delay, dq18 : 640 write_delay, dq19 : 640 write_delay, dq20 : 640 write_delay, dq21 : 640 write_delay, dq22 : 640 write_delay, dq23 : 640 write_delay, dq24 : 640 write_delay, dq25 : 640 write_delay, dq26 : 640 write_delay, dq27 : 640 write_delay, dq28 : 640 write_delay, dq29 : 640 write_delay, dq30 : 640 write_delay, dq31 : 640 Calibration Registers: CAL_OBS_0: 0x008136d6 CAL_OBS_2: 0x00813793 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00136d64 CAL_OBS_5: 0x00137938 CAL_OBS_6: 0x00f36d6f CAL_OBS_7: 0x03f3793f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0390 phy_grp1_slave_delay_0: 0x0390 phy_grp2_slave_delay_0: 0x0390 phy_grp3_slave_delay_0: 0x0390 phy_grp0_slave_delay_1: 0x0390 phy_grp1_slave_delay_1: 0x0390 phy_grp2_slave_delay_1: 0x0390 phy_grp3_slave_delay_1: 0x0390 phy_top_train_calib_error_info: 0x00000001 Training Results; Frequency 1; CS 1 PHY Vref Training: DQ Lane 0 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 1 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 2 Vref Mode: 0x7 Vref Sel: 0x2b DQ Lane 3 Vref Mode: 0x7 Vref Sel: 0x2b ACC Vref Control: 0x7ab CA Training: LP4 CA Programmed Delays: CA Bit 0 delay: 300 CA Bit 1 delay: 300 CA Bit 2 delay: 300 CA Bit 3 delay: 300 CA Bit 4 delay: 300 CA Bit 5 delay: 300 Write Leveling: DQ Lane 0 WRDQS: 0x0 DQ Lane 1 WRDQS: 0x0 DQ Lane 2 WRDQS: 0x0 DQ Lane 3 WRDQS: 0x0 DQ Lane 0 Write Path Latency Add: 0x0 DQ Lane 1 Write Path Latency Add: 0x0 DQ Lane 2 Write Path Latency Add: 0x0 DQ Lane 3 Write Path Latency Add: 0x0 Gate Training: DQS Gate Lane 0 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 1 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 2 : slave_delay: 109 lat_adj: 5 DQS Gate Lane 3 : slave_delay: 109 lat_adj: 5 Read Leveling: read_delay_fall, dq0 : 160 read_delay_rise, dq0 : 160 read_delay_fall, dq1 : 160 read_delay_rise, dq1 : 160 read_delay_fall, dq2 : 160 read_delay_rise, dq2 : 160 read_delay_fall, dq3 : 160 read_delay_rise, dq3 : 160 read_delay_fall, dq4 : 160 read_delay_rise, dq4 : 160 read_delay_fall, dq5 : 160 read_delay_rise, dq5 : 160 read_delay_fall, dq6 : 160 read_delay_rise, dq6 : 160 read_delay_fall, dq7 : 160 read_delay_rise, dq7 : 160 read_delay_fall, dq8 : 160 read_delay_rise, dq8 : 160 read_delay_fall, dq9 : 160 read_delay_rise, dq9 : 160 read_delay_fall, dq10 : 160 read_delay_rise, dq10 : 160 read_delay_fall, dq11 : 160 read_delay_rise, dq11 : 160 read_delay_fall, dq12 : 160 read_delay_rise, dq12 : 160 read_delay_fall, dq13 : 160 read_delay_rise, dq13 : 160 read_delay_fall, dq14 : 160 read_delay_rise, dq14 : 160 read_delay_fall, dq15 : 160 read_delay_rise, dq15 : 160 read_delay_fall, dq16 : 160 read_delay_rise, dq16 : 160 read_delay_fall, dq17 : 160 read_delay_rise, dq17 : 160 read_delay_fall, dq18 : 160 read_delay_rise, dq18 : 160 read_delay_fall, dq19 : 160 read_delay_rise, dq19 : 160 read_delay_fall, dq20 : 160 read_delay_rise, dq20 : 160 read_delay_fall, dq21 : 160 read_delay_rise, dq21 : 160 read_delay_fall, dq22 : 160 read_delay_rise, dq22 : 160 read_delay_fall, dq23 : 160 read_delay_rise, dq23 : 160 read_delay_fall, dq24 : 160 read_delay_rise, dq24 : 160 read_delay_fall, dq25 : 160 read_delay_rise, dq25 : 160 read_delay_fall, dq26 : 160 read_delay_rise, dq26 : 160 read_delay_fall, dq27 : 160 read_delay_rise, dq27 : 160 read_delay_fall, dq28 : 160 read_delay_rise, dq28 : 160 read_delay_fall, dq29 : 160 read_delay_rise, dq29 : 160 read_delay_fall, dq30 : 160 read_delay_rise, dq30 : 160 read_delay_fall, dq31 : 160 read_delay_rise, dq31 : 160 Write DQ Training: write_delay, dq0 : 640 write_delay, dq1 : 640 write_delay, dq2 : 640 write_delay, dq3 : 640 write_delay, dq4 : 640 write_delay, dq5 : 640 write_delay, dq6 : 640 write_delay, dq7 : 640 write_delay, dq8 : 640 write_delay, dq9 : 640 write_delay, dq10 : 640 write_delay, dq11 : 640 write_delay, dq12 : 640 write_delay, dq13 : 640 write_delay, dq14 : 640 write_delay, dq15 : 640 write_delay, dq16 : 640 write_delay, dq17 : 640 write_delay, dq18 : 640 write_delay, dq19 : 640 write_delay, dq20 : 640 write_delay, dq21 : 640 write_delay, dq22 : 640 write_delay, dq23 : 640 write_delay, dq24 : 640 write_delay, dq25 : 640 write_delay, dq26 : 640 write_delay, dq27 : 640 write_delay, dq28 : 640 write_delay, dq29 : 640 write_delay, dq30 : 640 write_delay, dq31 : 640 Calibration Registers: CAL_OBS_0: 0x008136d6 CAL_OBS_2: 0x00813793 CAL_OBS_3: 0xb3000000 CAL_OBS_4: 0x00136d64 CAL_OBS_5: 0x00137938 CAL_OBS_6: 0x00f36d6f CAL_OBS_7: 0x03f3793f CS Programmed Delays: phy_grp0_slave_delay_0: 0x0390 phy_grp1_slave_delay_0: 0x0390 phy_grp2_slave_delay_0: 0x0390 phy_grp3_slave_delay_0: 0x0390 phy_grp0_slave_delay_1: 0x0390 phy_grp1_slave_delay_1: 0x0390 phy_grp2_slave_delay_1: 0x0390 phy_grp3_slave_delay_1: 0x0390 phy_top_train_calib_error_info: 0x00000001 DRAM VREF Values: mr12_f1_cs0: 0x0000002a mr12_f1_cs1: 0x00000010 mr12_f1_cs2: 0x0000002a mr12_f1_cs3: 0x00000010 mr12_f2_cs0: 0x00000027 mr12_f2_cs1: 0x00000027 mr12_f2_cs2: 0x00000027 mr12_f2_cs3: 0x00000027 mr14_f1_cs0: 0x0000000f mr14_f1_cs1: 0x0000000f mr14_f1_cs2: 0x0000000f mr14_f1_cs3: 0x0000000f mr14_f2_cs0: 0x0000000f mr14_f2_cs1: 0x0000000f mr14_f2_cs2: 0x0000000f mr14_f2_cs3: 0x0000000f PHY IO Pad TERM Registers: PHY_1320: 0x000136d6 PHY_1321: 0x000136d6 PHY_1322: 0x000136d6 PHY_1323: 0x000136d6 PHY_1324: 0x000136d6 PHY_1325: 0x00013793 PHY_1326: 0x00013793 PHY_1327: 0x000136d6 PHY_1328: 0x000136d6 Enhanced Error Reporting: DQS Gate Error: 0 Training Error: 1 FSM Tran Error: 0 PLL Error: 0 Parity Error: 0 Timeout Error: 1 Timeout Error Info: dfi_rddata_valid Timeout: 0 Max PLL lock assertion Timeout: 1 Min PLL lock assertion Timeout: 0 DFI PHY master interface Timeout: 0 dfi_phyupd_req (PI - PHY) Timeout: 0 dfi_phyupd_req (CTL - PHY) Timeout: 0 dfi_lp_ack Timeout: 0 DFS change @ PI - PHY Timeout: 0 DFS change @ CTL -PHY Timeout: 1 CA / CS training Timeout: 0 WRLVL training Timeout: 1 RDGATE training Timeout: 0 RDDATA training Timeout: 0 WDQ training Timeout: 0 Training Error Info: 0x00007e00 Data Slice Error Info (bits [4:0]): Byte0: 0x00000108 Byte1: 0x00000108 Byte2: 0x00000108 Byte3: 0x00000108 PLL Frequency Error: 0x0