- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi expert,

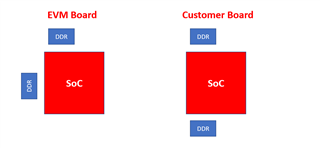

Due to some structure limitation, our customer cannot follow the DDR placement of EVM and have to move one DDR from left side to the bottom side as shown below. Our customer would like to know:

1. they can ensure each DDR satisfy the DDR layout guide. But there is a big length difference between these 2 DDR chips trace. Is there any risk for that?

2. what's the other comments or suggestions TI can share about their DDR placement?

Best Regards,

Xingyu Zhu

Regarding trace length requirements, there is no relationship between the two DDR interfaces. They are independent. TI has not done any evaluation of the proposed placement for the DDR memory device and its unclear what routing challenges will arise due to the placement. Recommendation is to follow the Jacinto7 LPDDR4 guidelines, and minimize any deviation. Trace lengths will likely increase beyond those recommended, and customer will have to decide to take those risks. Its possible bus frequency will need to be relaxed - again depending on the amount of deviation from our reference.