Other Parts Discussed in Thread: TMDX654IDKEVM

Hello,

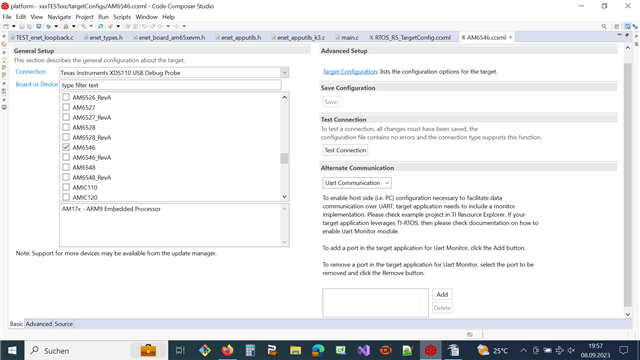

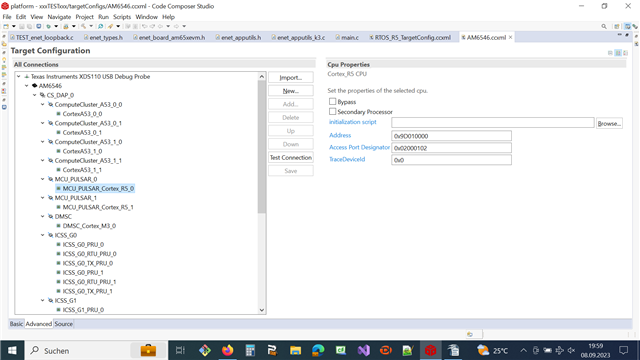

on our Target HW the SOC AM6546 is not responding on request from the XDS110 Debug probe.

XDS 110 Debug Probe is connected als follows:

1 o -------------- TMS

3 o -------------- TDI

5 o -------------- 3.3V

7 o -------------- TDO

11 o -------------- TCK

2 o -------------- RESET

10 o -------------- GND

Before we switched over to our Target HW we were using the TMDX654IDKEVM Evaluation Board.

I tested the XDS 110 Debug Probe with exactly the same connection as described above plus an additional line on pin 8 called SEL_XDS110_INV.

This line is nedded to switch off the onboard JTAG adapter and to enable the external JTAG

The XDS110 Debug Probe connected to the JTAG connector works fine. I can connect, load SW and debug it.

I checked the JTAG signals with a logic analyzer and I see all JTAG signals

On the Target HW I see the following:

- RESET goes HI

- TCK starts

- Test Logic Reset (more than 40msec)

- Then Signals on TMS and TDI

- TDO stays continously HI

The decodes JTAG protocol is added as file Target_HW_JTAG_Protocol.txt. See at the end.

The TDO line is all the time on 3.3V. Then I connected a 4.7kOhm resistor from TDO to GND and I measure a voltage of 0.5V.

TDO is of type output or tri-state. So if it is an output I think I should measure a value above 3V. And if it is in tri-state I should measure a voltage of 0V. So it looks that there is TDO not enabled on the SOC. If I calculate it back it looks like that there is a pull-up resistor of 26kOhm connected to TDO.

The EMU0 and EMU1 pins are connected to 3.3V via 22kOhm resistors. Except the EMU0 and EMU1 we have no HW BOOT-MODE configuration. So what is the Default boot-mode ? Is JTAG availabel in this case?

Thanks in advance and best regards

Ron