Team,

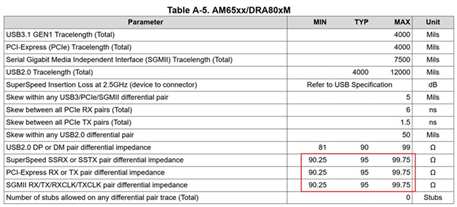

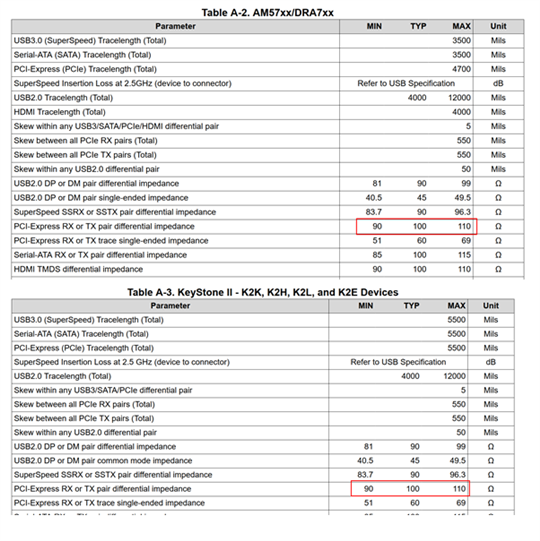

In AM65x “Application Note: High-Speed Interface Layout Guidelines”, the requirement for PCIe differential impedance control of AM6548 is 95Ω±5% , in AM57x and K2, the value is ±10% ,

Customer want to know the reason, and can they use ±10%, as the stricter standard will lead to a significant PCB cost increase.

-Thanks

Thomas