Hi TI Experts,

I have the below queries regarding Power supply sequencing between SOC (Processor) and the Attached devices

- Can I power the SOC (Processor) IOs and Attached devices from different power sources?

- Is there a recommended power sequencing requirement to be followed between the SOC (Processor) and the attached devices?

- I have a modular design. I have the attached devices on the carrier board and the SOC (Processor) on the SOM board. Any power sequencing recommendations?

- Is there a recommendation to be followed when the SOC (Processor) and the attached devices are powered from different sources?

- Are these recommendations applicable for all the Sitara family of devices?

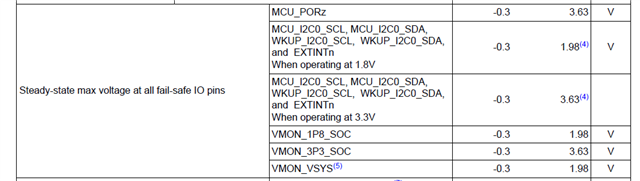

- Examples of failsafe IOs

Let me know your thoughts.