Part Number: AM3358

Other Parts Discussed in Thread: AM3354

Hello Champs,

SW: linux kernel5.10

Customer is transmitting data using the infrared serial port, using the 8250 driver with interrupt mode, the other side is stm32. The uart idle interrupt is used to detect if the am335x has sent data, and when a 2-character interval greater than a fixed value is detected, the am335x is considered complete!

There are now problems:

am3354 using interrupt transmission, often interrupted by other interrupts, resulting in data from xmit->buf to the infrared serial chip in the FIFO generated large delay, so stm32 mistaken the am3354 transmission data is over, Data loss in the end!

How to ensure that the uart interrupt transmission of am3354 is not interrupted abnormally, resulting in increased latency?

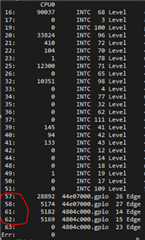

The specific thread was not found, and it is now assumed that the most likely interrupt priority is too low. When calling serial8250_handle_irq to interrupt the service, it is possible that a high priority preemptive run is made.

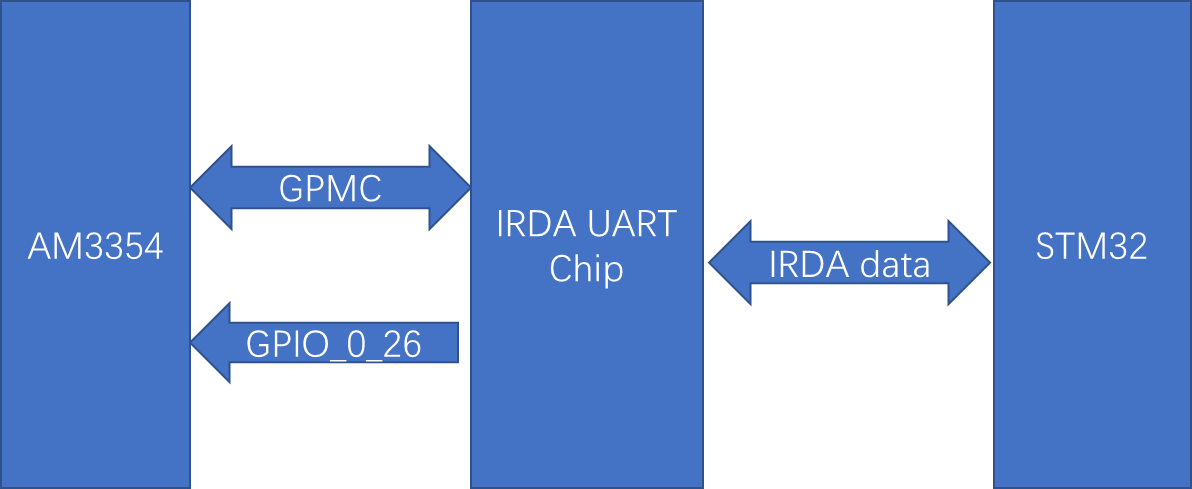

The serial port is attached to the external serial chip by way of GPMC; the interrupt of uart is triggered by the GPIO_0_26, this IO level changes, they send data to the uart FIFO or read data from the uart FIFO;

So is there a way to increase the interrupt priority for this GPIO port?

Thanks

Regards

Shine