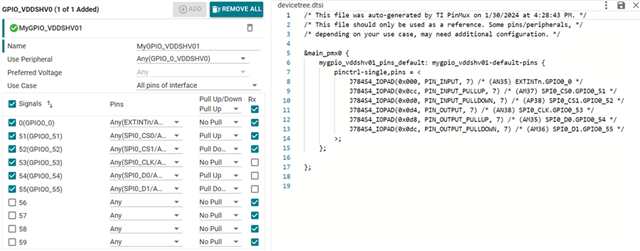

TI’s SysConfig PinMux Tool is a GUI interface which allows the user to select the desired device pin configurations for their system. The SysConfig PinMux Tool outputs customer-selected configurations in the following files:

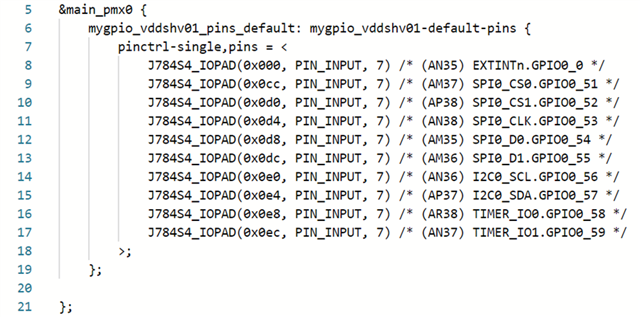

- devicetree.dtsi,

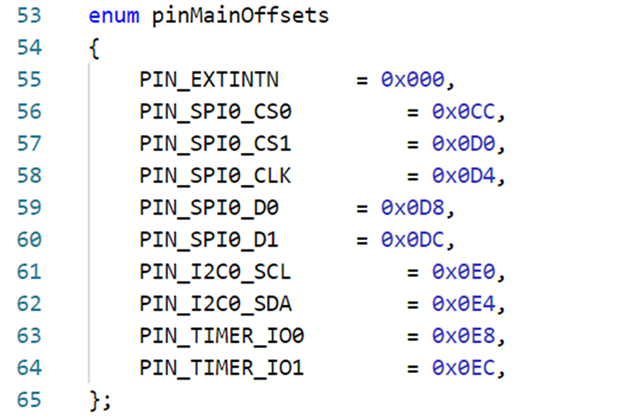

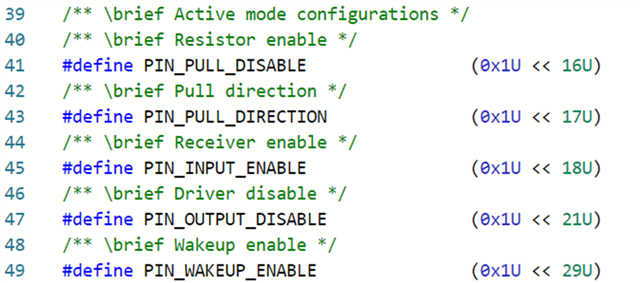

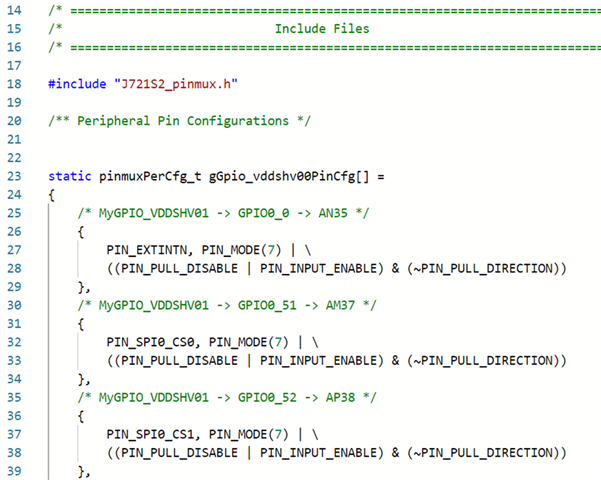

- <device>_pinmux.h, and

- <device>_pinmux_data.c

Where <device> corresponds to the superset name of the device.

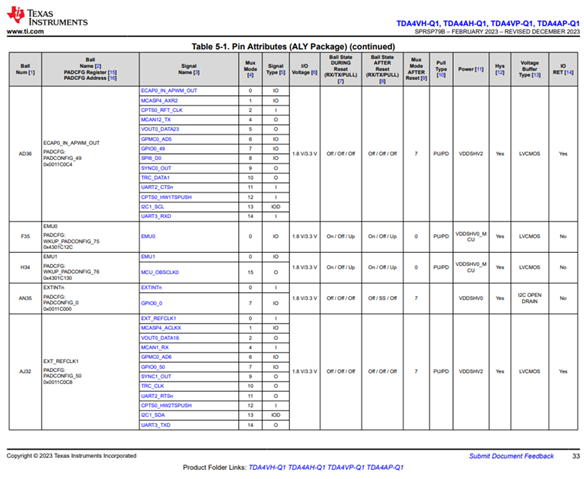

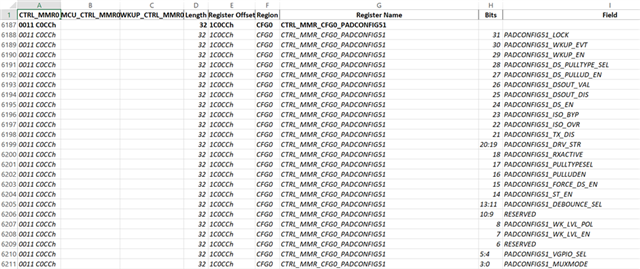

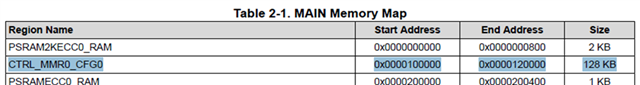

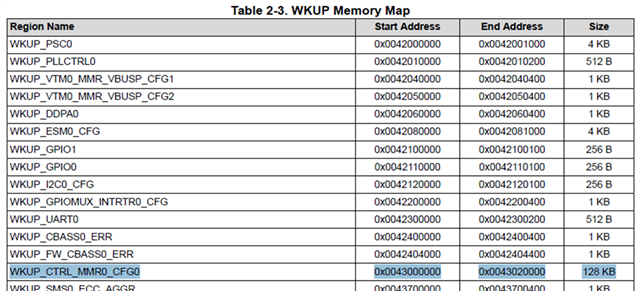

Here are some recommendations, using TDA4VH as an example, to validate the output files to a device’s respective datasheet and technical reference manual.