Hi,

SDK:8.6

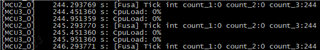

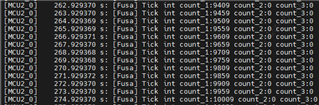

I need to use WKUP_GPIO8 and WKUP_GPIO70 in MCU2_0 to capture the rising interrupts.

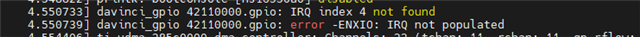

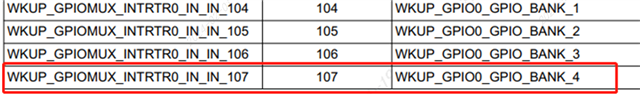

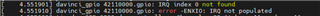

When I choose WKUP_GPIO8, belonging to banknum=0, interrupt can register successfully, but choose WKUP_GPIO70, belonging to banknum=4, failed to interrupt registration.

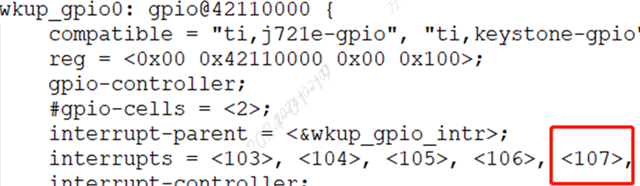

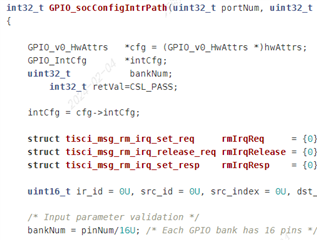

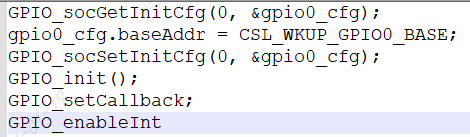

Here is the api for the gpio interrupt registration I used on mcu2_0.

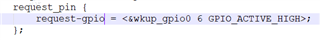

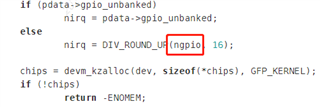

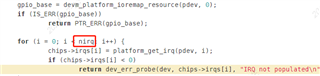

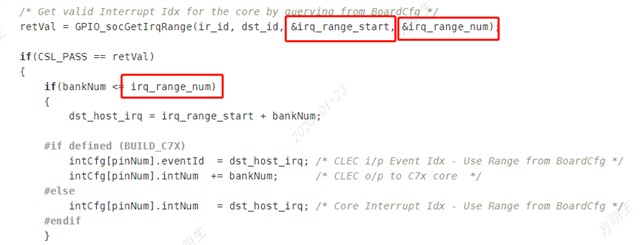

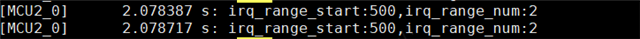

When I checked the PDK, I found some logical errors, as shown in the following figure. When banknum>2, it will never enter interrupt registration.

This means that when banknum>2, no GPIO can apply for interruption.

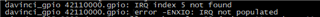

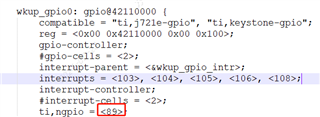

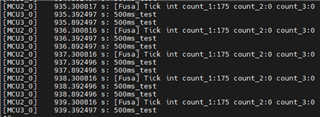

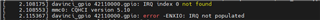

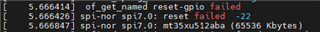

When I modified the judgment logic, I indeed applied for an interrupt, and MCU2_0 did indeed capture data from WKUP_GPIO70,but it caused the GPIO driver application on A72 to fail. When checking the error location, it was found that the registration of GPIO irq in the driver failed. May I ask what is the connection between these two?Does A72 cause this problem because MCU2_0 registered WKUP_GPIO interrupt?