Hi TI Experts,

I am designing my custom board using TI AM62x family of processors. I have a few queries.

1. I am expecting to not use some of the SOC peripherals. Do you have a recommendation?

2. We have a general recommendation to add a pull down to unused AM64x I/O that has test points on it. This is a bit unexpected for me to see as well. How critical is this. What if customer instead enables the internal weak pull-down, or configures the I/O as an output? Does that remove the need for an external pull-down.

3. Our assumption for the recommendations is that we are just wanting to prevent noise coupling onto the unterminated trace.

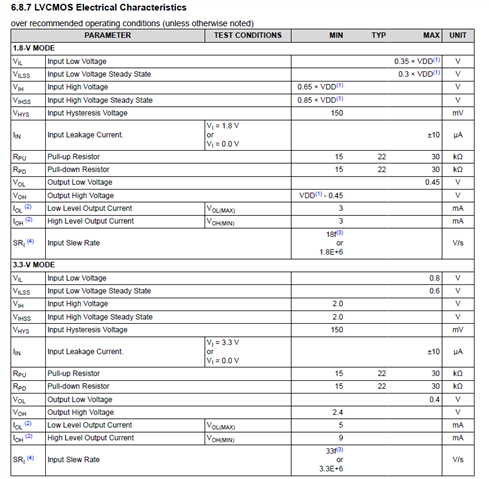

4. Is there any concern connecting a capacitor or connecting an external slow ramp input to the SOC IOs or Reset inputs.

5. Is it allowed to connect a capacitor at the output of the SOC IO