Hi Expert

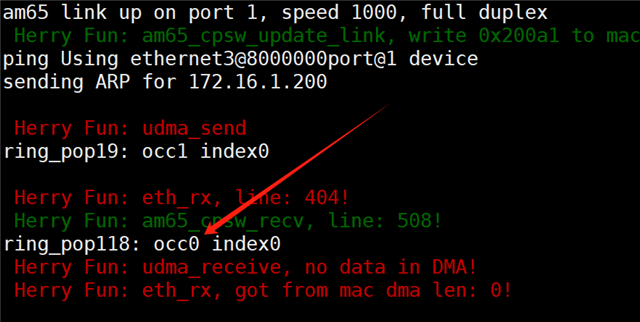

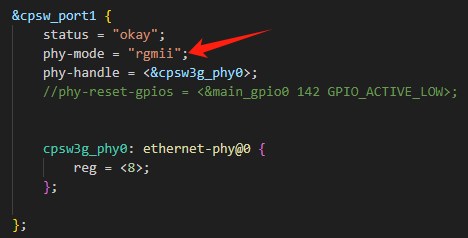

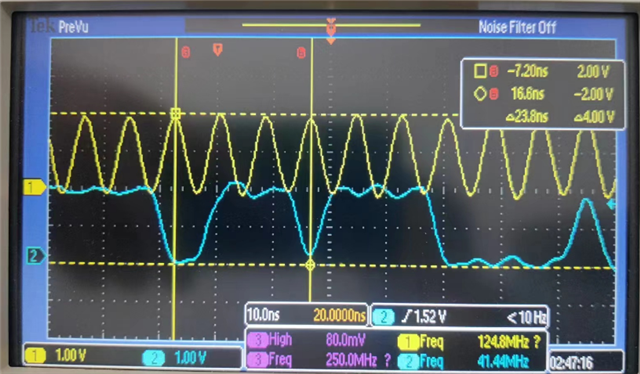

Now we have AM62 for BBU, i set to loopback mode to verify board is OK, beacuse CPPI can got data, but RINGCC is empty.

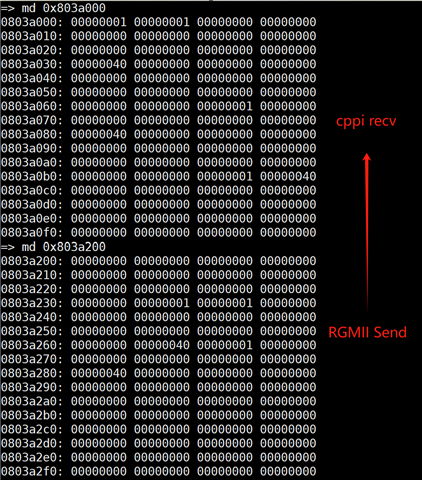

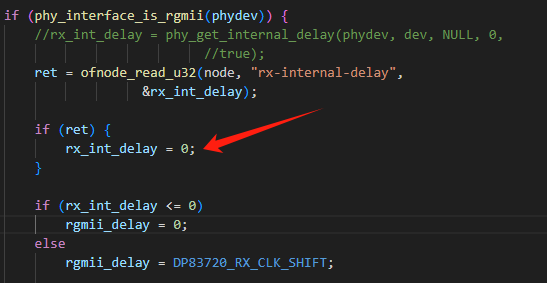

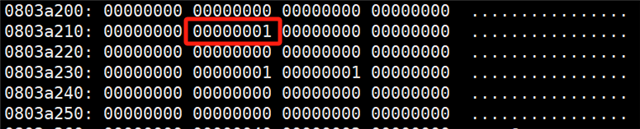

RGMII port1 send OK, 0x803a234 is 0x1, 0x803a264 is 0x40, at same time , CPPI port0 got same frame and bytes. 0x803a000 is 0x1, 0x803a230 is 0x40, so why RINGCC is empty? occupy flash always 0.

Thanks