Other Parts Discussed in Thread: SK-AM62, AM5718, AM3354

HI,

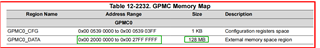

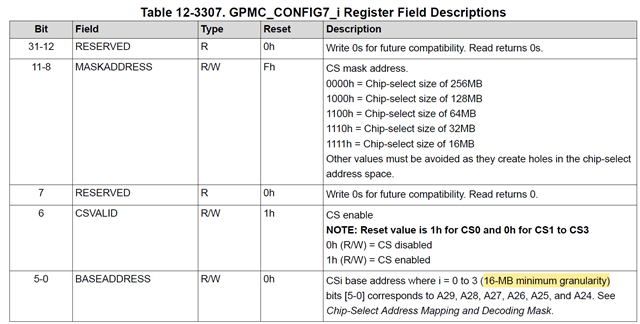

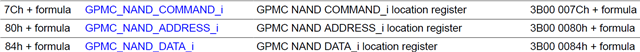

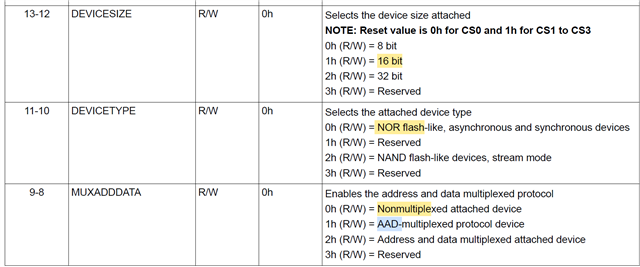

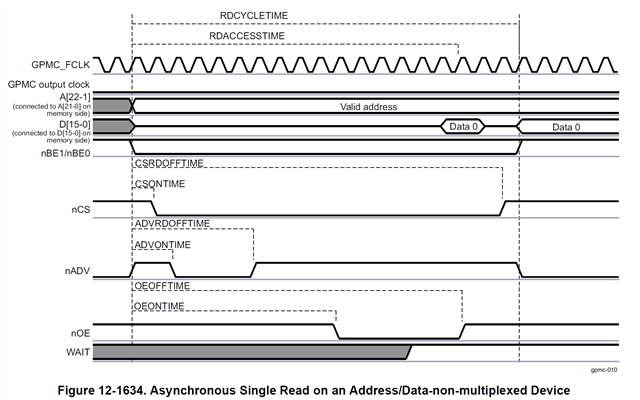

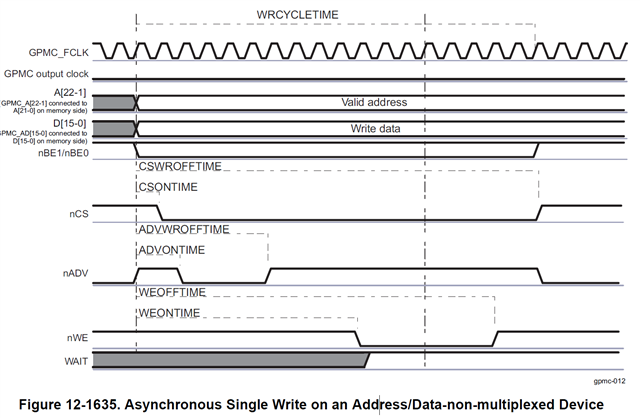

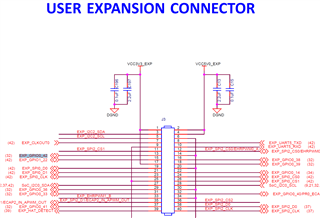

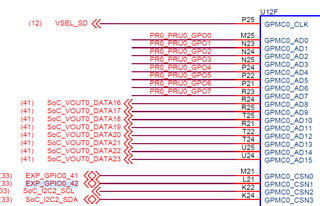

I have the problem on the GPMC interface. for hardware ,we have set cs0 for NAND (8 bit A/D multiplexed mode). cs2 for 256K sram (18bit ad lines ,16 bit D lines).

cs3 for 1M FPGA (20 bit AD lines ,16bit D lines).so how to cofigure GPMC in the dts ?

just configure the GPMC for NAND, the nand works oK .

so we want to know how to configure sram and fpga at the same time .

hope your advices as soon as possible .

Thanks !