Other Parts Discussed in Thread: DRA821

Does this link also apply to DRA821 part for In-Line LPDDR4 ECC setup?

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Does this link also apply to DRA821 part for In-Line LPDDR4 ECC setup?

Hi,

Due to a holiday, half of our team is currently out of the office. Please expect a 1~2 delay in responses.

Apologies for the delay, and thank you for your patience.

-Fabiana

Hi Syed,

Do you want to enable inline ecc for DDR in the R5 SPL?

Please go through:

e2e.ti.com/.../tda4vm-how-to-enableti-s-inline-ecc-for-ddr-when-ddr-size-is-3gb

The AM64 SoC is different so kindly elaborate your use case? What's the end goal?

Best Regards,

Keerthy

Hello Keerthy,

We have external 8Gb 1x32 dual channels (single rank) IS43LQ32256A-062BLI LPDDR4 connected with DRA821 Memory Subsystem. We want to test the performance with and without in-line ECC. We are currently running LPDDR4 without In-Line ECC, so it will be great if you can share how to enable and test In-line ECC on LPDDR4 with DRA821. Knowing how to test In-Line ECC will be very useful. We are running U-BOOT and VxWorks images on DRA821.

Regards,

Syed

Hi Syed,

Do you have the DDR working without ecc? That will be my first question. Let us know.

Best Regards,

Keerthy

Hi Syed,

The inline ecc enabling should be almost same for Dra821 as well. Please follow the above thread.

Best Regards,

Keerthy

Hey Keerthy,

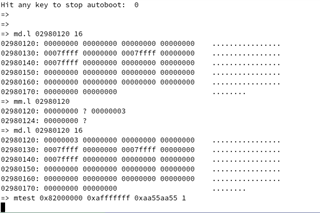

Looking at the thread you posted, to enable in-line ECC for the DDR, we would need to implement that patch into our SDK? Is there not any additional work that's needed to enable ECC in U-Boot? We tried changing the registers directly in U-Boot to enable ECC, but every time we would do that, U-Boot would freeze, so looking for other ways to enable DDR ECC.

Also I have some additional ECC related questions:

Does TI has any recommended ways to test in-line ECC?

Does the LPDDR4 Driver has in-line ECC?

Are we sacrificing 32 bits (losing 8 bits to In-line ECC) and actually getting 24 bits with In-line ECC? If so, do we need to do anything on software side to read data correctly?

Thanks,

Lewis

Lewis,

Please port the patch to your code base. These writes need to be written from R5 SPL phase as it executes out of internal sram and not from DDR. In the case of U-Boot that itself is executing out of DDR and you are tampering with DDR runtime and the behaviour you observe is expected.

The inline ecc for DDR needs to be configured in. The R5 SPL.

Best Regards,

Keerthy