Part Number: AM3352

Tool/software:

Hi Support Team,

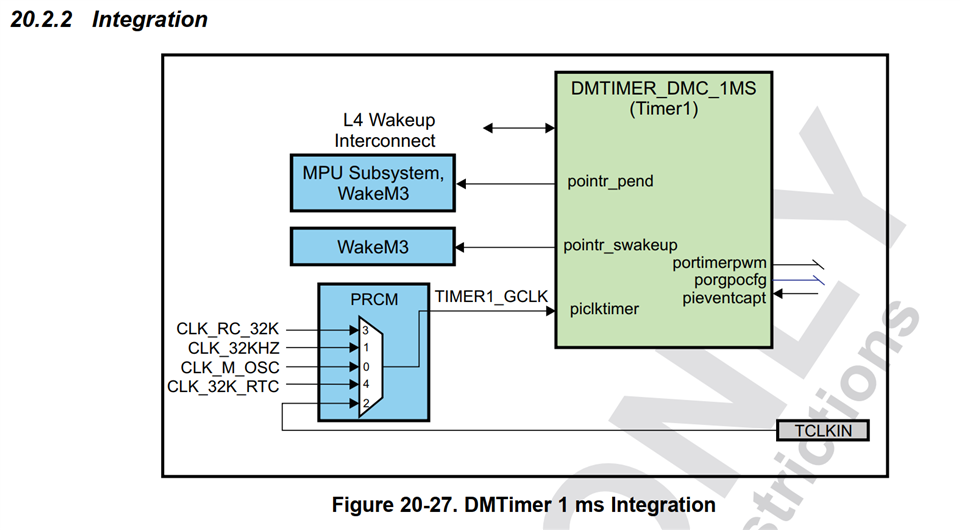

I have been asked about the DMTimer 1ms by a customer who uses the AM3352.

We are currently developing a model that uses this timer and interrupts at 1msec intervals,

but for some reason, this interrupt may not be triggered.

Counter Register (TCRR) itself is counting up normally,

but when it goes OverFlow and reaches the value in the Load Register (TLDR),

the OVF_IT_FLAG bit in the Status Register (TISR) does not hit, and the interrupt is not triggered.

This state is called "no interrupts".

Also, in this state, TOCR is counting up.

TRM: 20.2.3.1.1.1 1 ms Tick Generation describes the following,

but I cannot find a description of what triggers the filtering.

> The Timer Overflow Counter Register (TOCR) and the Timer Overflow Wrapping Register (TOWR) are used for interrupt filtering.

The following description is given in the NOTE section, which also recognizes that the 5 registers

are used in their default state (all 0s), so the function of this correction is turned off.

> By default, the TPIR, TNIR, TCVR, TOCR, TOWR registers and the associated logic are in reset mode (all 0s)

and have no action on the programming model of the DMtimer_dmc1ms.

Could you please tell me what triggers the interrupts to be filtered?

Please contact me if you have any clarification or information needed.

Best Regards,

Kanae