Other Parts Discussed in Thread: DRA821, SYSCONFIG

Tool/software:

Dear Team,

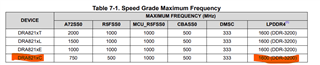

DRA821U datasheet suggests speed grade for LPDDR4 is 1600 (DDR-3200)

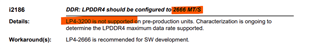

But errata suggests revision1 processor has speed limitation of 2666 MT/S which is solved in production boards revision 2

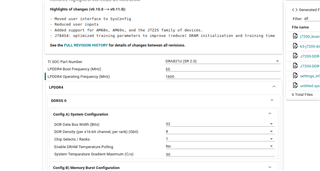

But we are using DRA821U2CGBALMR SoC with SDK Version: 09.02.00.04 which is latest one also has 2666 MT/S. When checked in our board, our board boots fine with 2666 MT/S speed but when changed to board hangs. Should we continue with 2666 MT/S instead of 3200MT/S. Also why is latest SDK having 2666 MT/S instead of 3200MT/S.

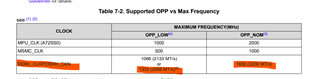

Also please say DRA821U2CGBALMR is OPP_LOW or OPP_NOM supported?

Regards,

Kaushal