Tool/software:

Hi, TI:

The DPI of the AM623 DSS we use is connected to a 10.1-inch 24-Bit RGB LCD. When testing the EMC RE of the current product, it was found that the LCD_PCLK radiation emission of the DPI port of the AM623 DSS is very strong.

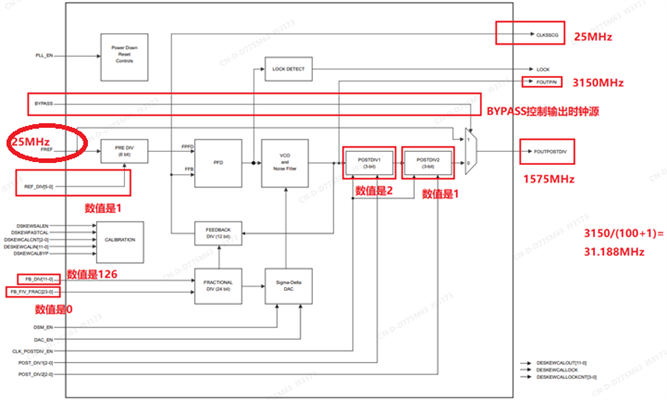

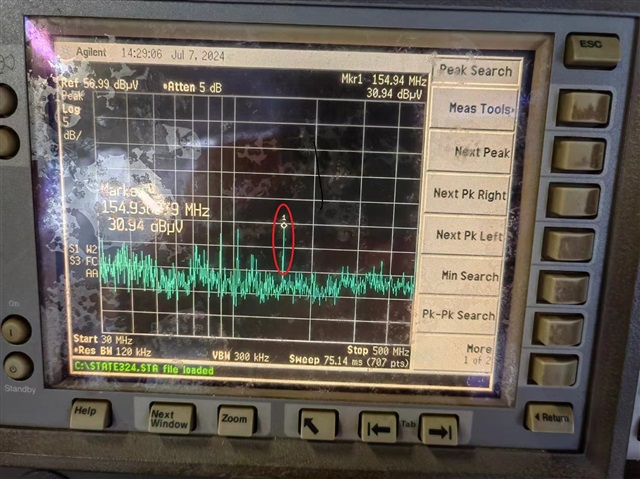

For example: When testing the LCD_PCLK clock is 31.2MHz, it is found that there is a strong spike at the 5x frequency 155MHz, as shown below:

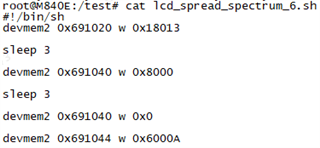

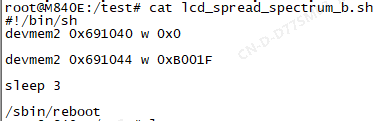

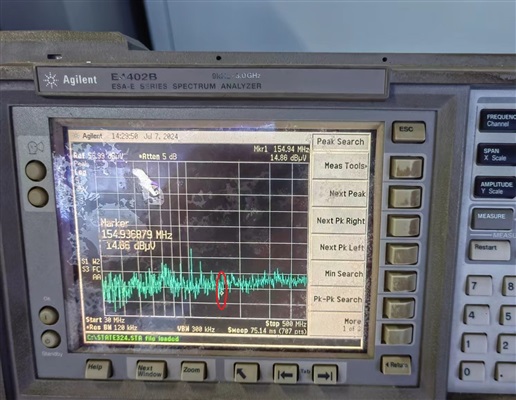

When we use the spread spectrum of PLL17, the test found that after the spread spectrum is turned on, the 155MHz spike basically disappears in the background noise, as shown below:the current spread spectrum design is to make it effective by changing the register and then soft restarting.

The EMC RE problem of LCD PCLK of AM623 is very difficult to solve. Using near-field scanning, it is found that the emission of the clock signal is very strong. Please ask TI to help solve it. In addition to the spread spectrum, can the strength of the LCD_PCLK signal be reduced?

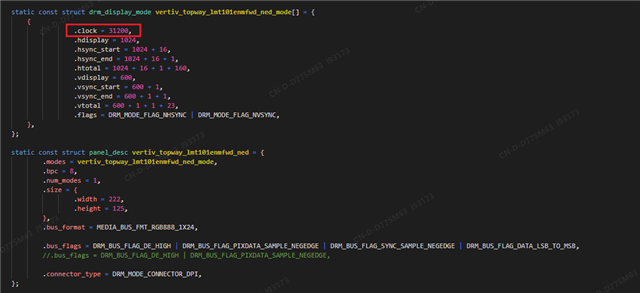

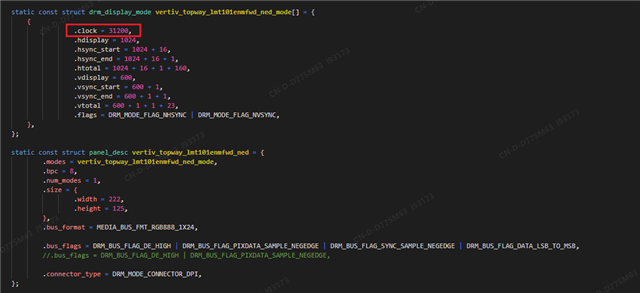

In addition, there is another problem. When modifying the LCD_PCLK clock of panel-simple.c, it is found that when LCD_PCLK is set to a certain clock, after the modified kernel is put into the device startup, LCD_PCLK is not the clock you want to set, but 25MHz, as shown below: set .clock to 33.5MHz, compile the kernel and run it in the device. The LCD_PCLK clock tested with an oscilloscope is 25MHz.