Tool/software:

Hi,

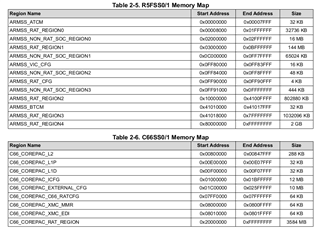

Tried to modify 00A0 0004h from C66xx_0.

Direct via:

*(unsigned int*)(0x00A00004) = 0x00010100;

(does not work)

and also via RAT:

HW_WR_REG32(0x60000004,0x12345678);

(does not work)

But: With RAT I can read the PID at 0x00A00000 to be 0x66948100.

I can modifiy the Address-Space (0x60000004) in Memory Browser of CCS !

I can read the modification made directly in Memory Browser of CCS with

Wolfgang = *(volatile unsigned int*)(0x60000004);

But I can't change the value from the CPU!

Any hints appreciated!

Wolfgang

P.S.: RAT defined:

CSL_RatTranslationCfgInfo translationCfg4Test3PurposeOnly;

CSL_ratRegs* pGTCRatRegs4Test3PurposeOnly = reinterpret_cast<CSL_ratRegs*>(CSL_C66_COREPAC_C66_RATCFG_BASE);

translationCfg4Test3PurposeOnly.sizeInBytes = 0x200;

translationCfg4Test3PurposeOnly.baseAddress = 0x60000000;

translationCfg4Test3PurposeOnly.translatedAddress = 0x00A00000; // GPIOMUX_INTRTR0_INTR_ROUTER_CFG

CSL_ratConfigRegionTranslation(pGTCRatRegs4Test3PurposeOnly, 4, &translationCfg4Test3PurposeOnly);

P.P.S.: I checked TSR and found CXM: 0 - hence, my code runs in "Supervisor mode".

P.P.P.S.: I'm aware that not all bits can be written at that target. Hence, above "0x12345678" will not be written.