Tool/software:

Hi, Ti Expert

if pipeline depth is set to 1, the tidl results of each frame are correct. but the pipeline depth is changed to 2

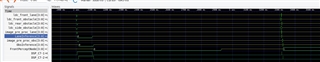

you can also have a look at the picture above, you can see that the pipeline 0 work normally, but the pipeline 1 does not spend any time on tidl. so it seems that the pipeline 1 was not trigggered to run

the same application code can work normally in j721s2 8.5sdk 8.6sdk

Is there some issue in the j784s4 sdk 9.2?

Looking forward to your replay!

Thanks