Tool/software:

Hi,

We are using version 8.6 of SDK.

We added some of our business code to the SBL, and the link failed at compile time.

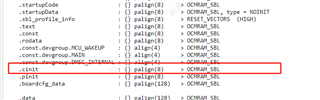

Failed log:

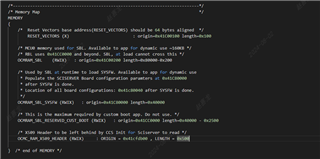

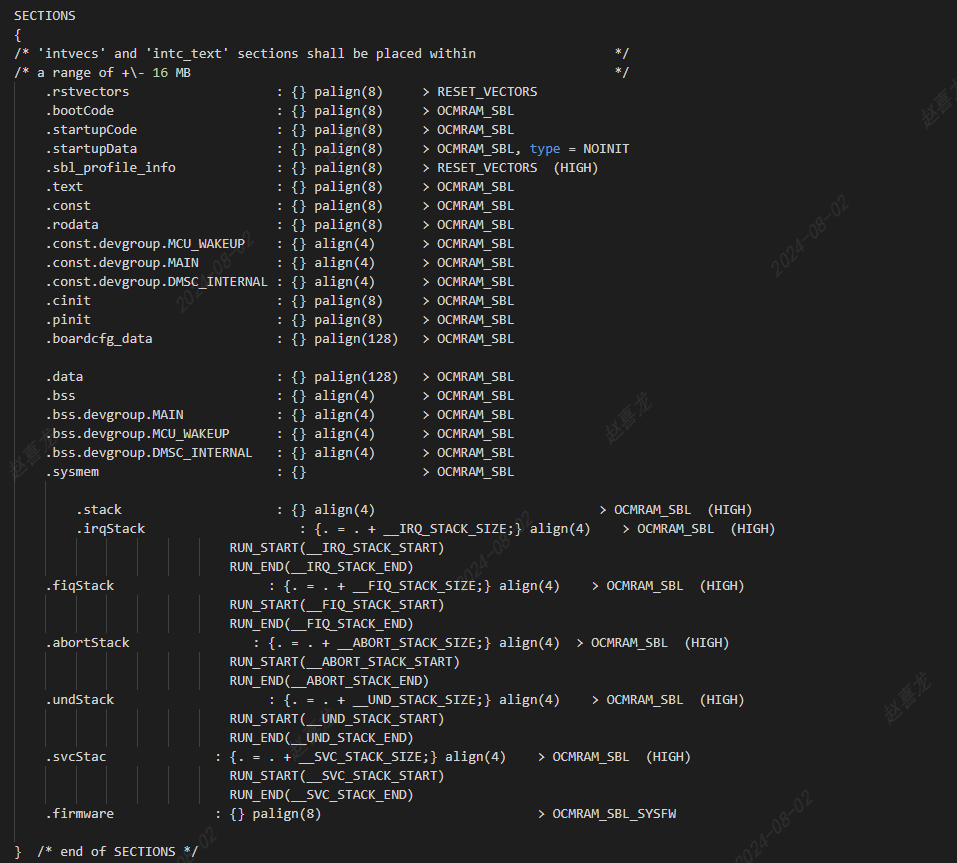

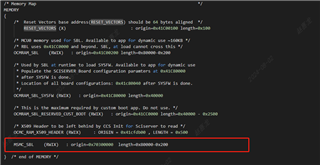

lds file:

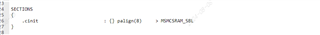

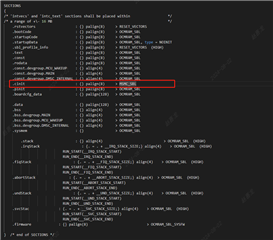

To solve this problem, we want to put the cinit segment into MSMC.

The changed lds file:

This change can be compiled, but the resulting image is too large, about 700M in size.