Part Number: TDA4VH-Q1

Tool/software:

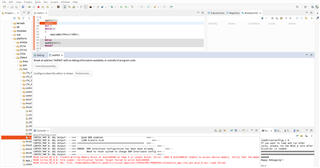

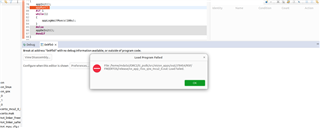

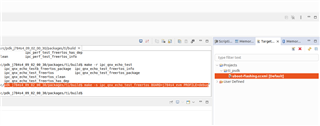

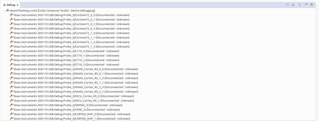

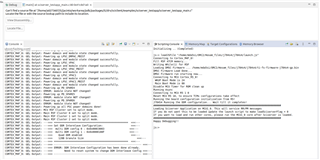

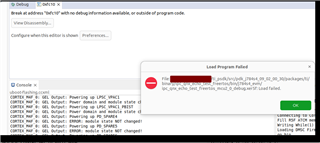

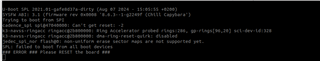

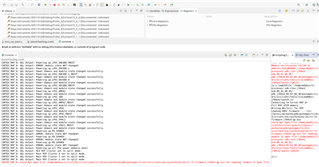

I followed the instructions provided in the documentation Setting up CCS But when i launch the launch script i get following error.

I also donot have the ti-fs-firmware-j784s4-gp.bin binary in the folder. How can i get this binary. Can anyone please help fix itl