Other Parts Discussed in Thread: SYSCONFIG

Tool/software:

Hi TI experts,

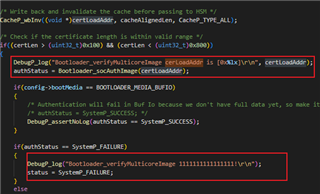

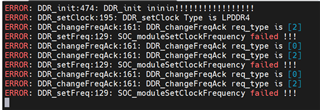

We will replace the DDR on EVM with Samsung's DDR(4G K4FBE3D4HB-KHCLT2V), Rename the generated file as board_ddrReginit.h and replace the original board_ddrReginit.h.But sbl failed to start as shown in the screenshot below.Can you help me confirm if it is caused by incorrect parameter configuration?

Regards.