Other Parts Discussed in Thread: SYSCONFIG, TDA4VL

Tool/software:

Dear TI

We would like to use CCS to run .out file to check

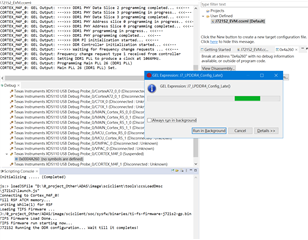

However, we stop at the "J721S2 Running the DDR configuration... Wait till it completes!"

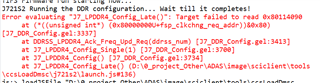

and have following error log

Do you have any comment?

We use pdk_j721s2_10_01_00_25 and with 8GB DDR memory(mt53e2g32d4de-046)

TI's default design seem 16GB,

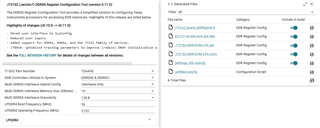

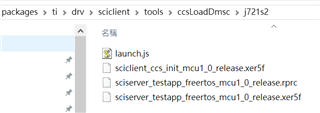

Should I need to do some modification and rebuild about sciclient_ccs_init_mcu1_0_release.xer5f and sciserver_testapp_freertos_mcu1_0_release.xer5f?

Thank you very much