Other Parts Discussed in Thread: ADS127L18, SYSCONFIG, TMDS64EVM

Tool/software:

Dear TI experts,

We have the following hardware configuration:

The two ADCs are attached to McSPI4 in multi-controller mode on an AM6442 SoC and are to be used on the R5F side. The requirements are as follows:

- 128 KSPS readout rate

- Sequential readout, first ADC1 and then ADC2. We have to be able to distinguish the data source, i.e., if the sample comes from ADC1 or ADC2

- Stable readout frequency - max. jitter 10ns

- Interrupt every 32 samples

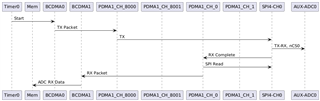

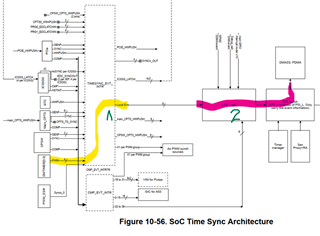

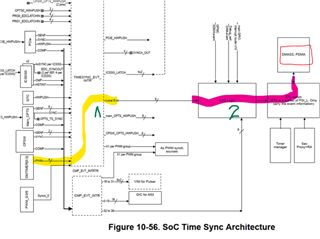

We already have another ADC, attached to the SoC (8-channel ADS127L18), which acts as an SPI master and generates nCS and clock for 2 McSPI in peripheral mode. This ADC is being read out through PKTDMA+PDMA, being triggered on an McSPI RX.

Our intention was to use either the nCS, generated from the ADS127L18 (internally, as an internal trigger, or externally, as a GPIO interrupt), or a timer to trigger a second DMA, which has to read both ADCs sequentially.

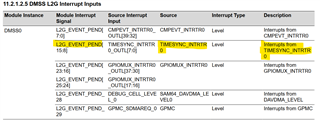

Please note that a timer interrupt is not an option here, as it will cause a significant amount of jitter, leading to distortion in the digitized signal. We need a stable readout frequency.

We have the following questions:

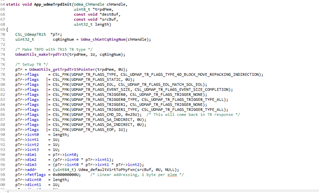

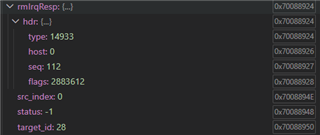

- Apparently, PKTDMA cannot be triggered from an arbitrary trigger source; it has to be a packet/event generated from a peripheral. That means that we have to use BCDMA, correct? Is the usage of BCDMA compatible with PDMA for McSPI?

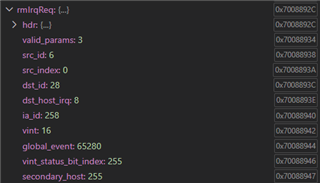

- What will be the way to configure the BCDMA to use an internal signal, such as RX Complete from another McSPI (for example, McSPI 3), which signal is used to trigger the DMA transfer from another McSPI?

- BCDMA has to be configured to read both ADCs, ADC1 and ADC2 sequentially, since they share the same McSPI. In theory, those are 2 separate SPI channels, but can the DMA be chained in such a way that:

- An external event (ADS127L18 nCS, GPIO interrupt, or a timer) triggers the readout of ADC1

- When completed, McSPI TX Complete of ADC1 triggers the readout of ADC2

- Do we probably need more than one BCDMA channel to achieve the above?

Thank you!