Hello,

Our custom project board has secured C6748 on it.

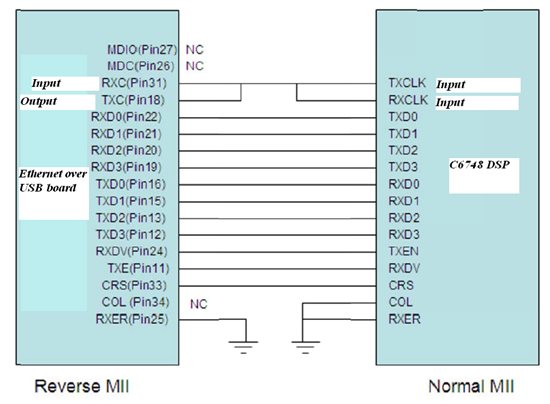

We have built the following setup for the Ethernet communication:

Where Reverse MII is third party manufacturer board, which performs Ethernet over USB conversion, and the Normal MII is the EMAC of the C6748.

Reverse MII board is powered by a PC via USB and the PC detects it as a network card (as expected).

If we connect the two boards( while the Reverse MII board is plugged by USB), the DSP crashes, so we cannot debug via the JTAG, and we have to reset the C6748.

In addition, we cannot connect via JTAG debugger when the two boards are connected (and powered).

- What can crash the DSP in this setup? If it is the TXCLK or RXCLK, then why and are they legally connected?

- Is this setup workable for the EMAC MII configuration to perform data transmission in general?