Dear TI,

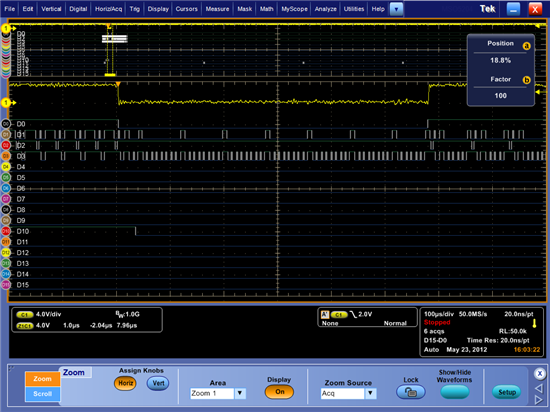

I need help on the EMIFA Timing when I have a DMA Transaction. I have attached an analyzer shot where the following are the symbols:

DO = Interrupt to the DSP

D1 = Chip Select

D2 = Write Strobe

D3 = Read Strobe (output enable)

You can see that before the interrupt that there is always a chipselect for each read/write transaction. During a DMA read transaction (the interrupt launches a DMA routine) the chipselect is held active during a sequence. However, we have another DMA transaction to write data out (image not attached, since I forgot to save it) and during that there is a chip select pulse for each write (e.g. chip select is not held active for contiguous write enable). I have dug through the 1800 spruh77 and found no reference that this should occur. You can see form our config below there should be at least on turnaround cycle but yet on the DMA read we are seeing zero.

My guess this is 100% expected..but where in the documentation does it say it?

void C6748_init_emifa( void )

{

/* CS2: FPGA */

AEMIF->A1CR = 0

| (1 << 26) /* W_SETUP = 1 */

| (3 << 20) /* W_STROBE = 3 */

| (1 << 17) /* W_HOLD = 1 */

| (0 << 13) /* R_SETUP = 0 */

| (6 << 7) /* R_STROBE = 6 */

| (0 << 4) /* R_HOLD = 0 */

| (0 << 2) /* TA = 0 (1 cycle turn-around) */

| (1 << 0) /* ASIZE = 1 (16-bit device) */

;