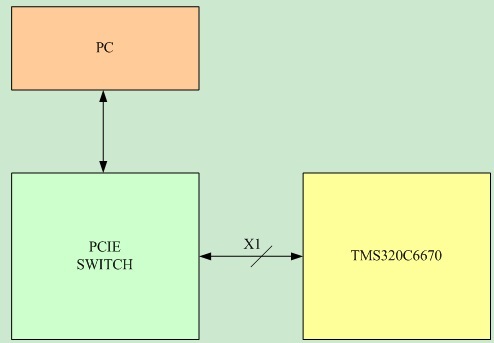

I have designed a PCB board by using TMS320C6670. The PCIE link architecture is showed in figure 1.

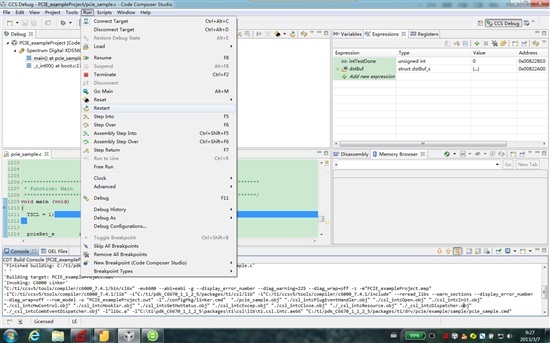

I use the PCIE_exampleProject to test the PCIE interface of the TMS320C6670. Because the PCIE link will break down, so I add some codes to monitor the value of the LTSSM_STATE in register DEBUG0. If LTSSM_STATE != 0x11, rebegin to link training by set LTSSM_EN = 1;

I reset the PC to test the PCIE link, the link is ok at the first two reset. But when I thirdly reset the PC, the LTSSM_STATE will always be 0x2.

Why?

Thank you!