Hi,

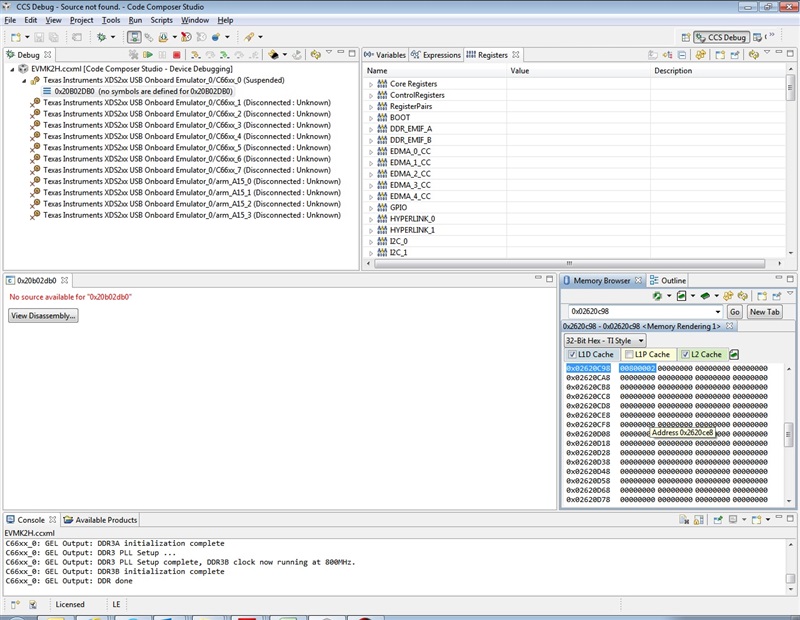

I'd like to confirm what I am getting is correct. I am using an EVMK2H board. The board features a single 66AK2H14 SoC chip, with 4X Cortex-A15 + 8X C66x cores. I set the board to boot from "No Boot/JTAG DSP Little Endian Boot" mode. I am using CCS 5.5.0.00077 and the onboard XDS2xx USB emulator to connect to the board.

When I connect to the target, and read from the DEVSPEED register, I get 0. That means both the ARM and DSP cores work at 800MHz. Is this expected? I'd appreciate if you could confirm, or point out what I am missing. Thanks!

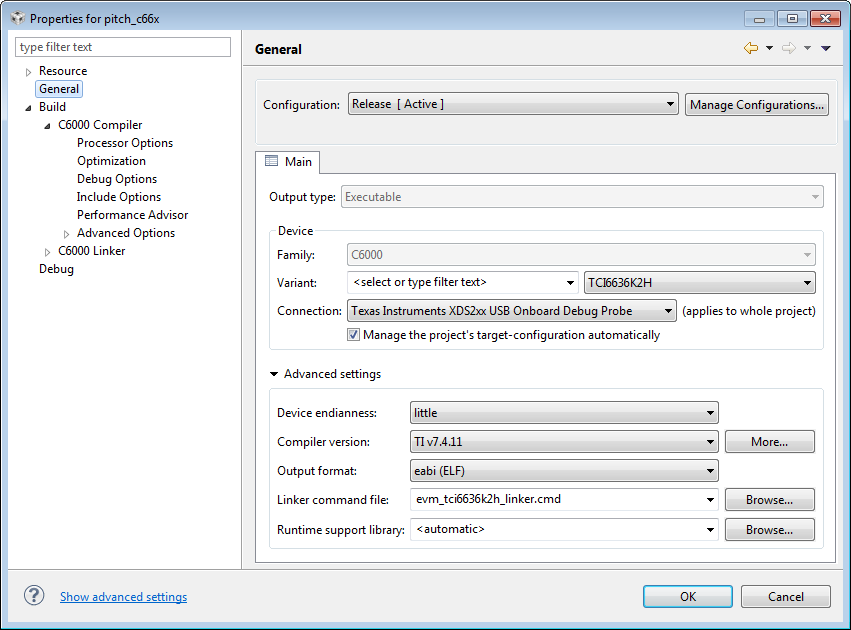

The target settings of my project are like this:

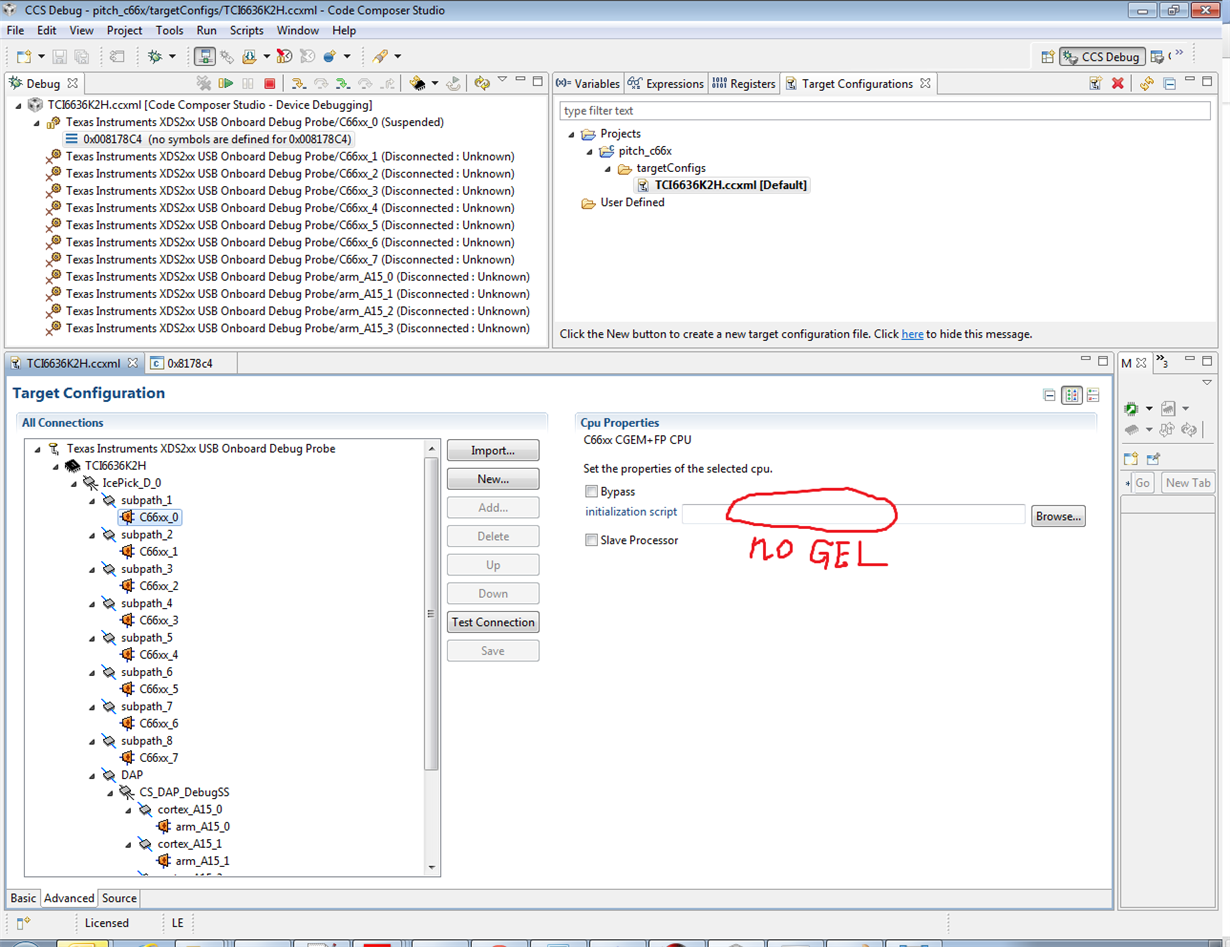

The target configuration is like this. You can see that there is no GEL file used to initialize the core. At least I didn't specify one: