Dear expert

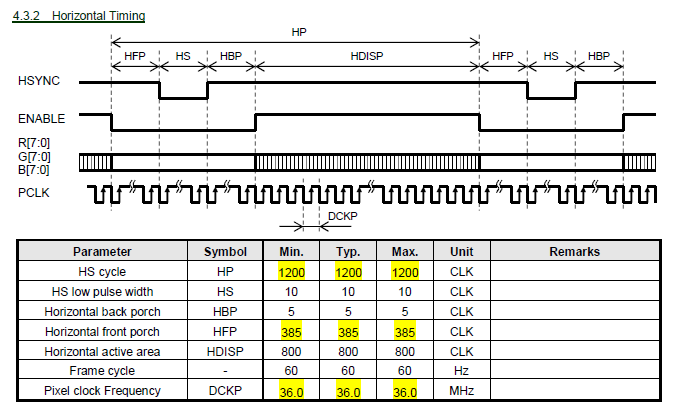

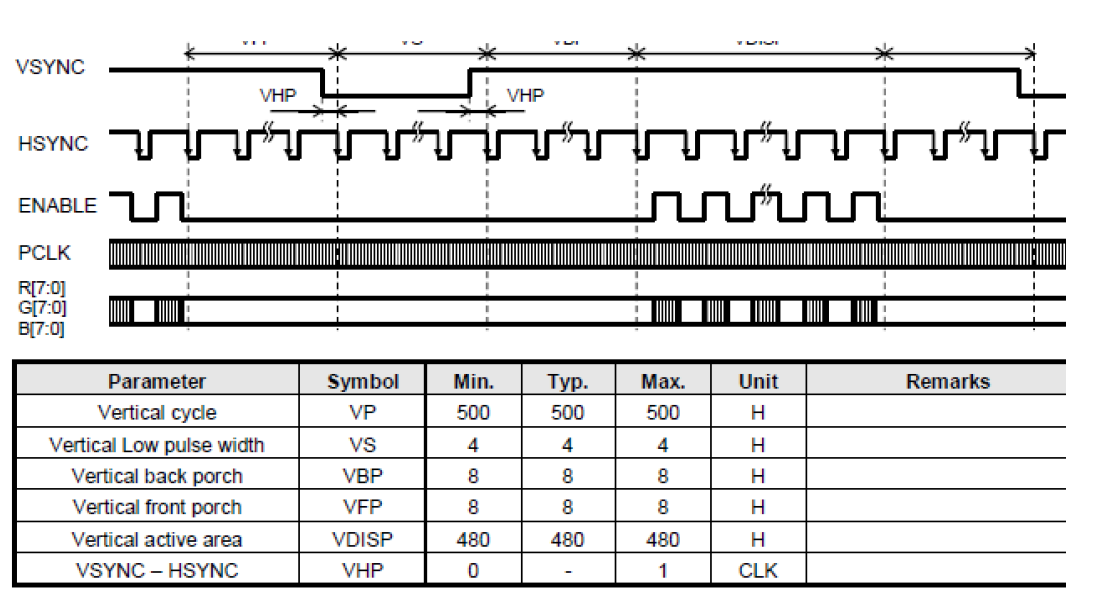

Our customer observed delay of HSYNC and VSYNC of vout is about 385 pclk in DRA64x. however the delay of HSYNC and VSYNC is expected to <1 pclk. Here is snapshot of HSYC and VSYNC. Did you have any idea to adjust the delay time? I have asked them to try invert polarity of VSYNC/HSYNC. It does NOT work.

Regards

Dong