Hi,

I have a question about the assert timing of WAIT signal for C6672.

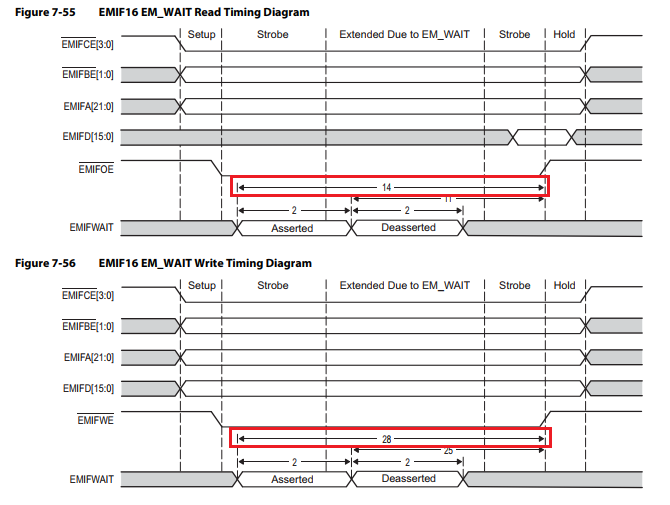

Q1: Is it defined the timing to assert the WAIT signal after the OE( or WE) singal becomes active?

Q2: The data manual defined about setup time of WAIT signals( #28 and #14 ) on Table 7-76. Does this mean that the WAIT signal must be asserted before 4E + 3 where OE ( or WE) is deasserted?

Best regards,

H.U