Team,

Could you please confirm that the below use case are supported in the AM57x PCIe when used as EP and by the associated Linux drivers too.

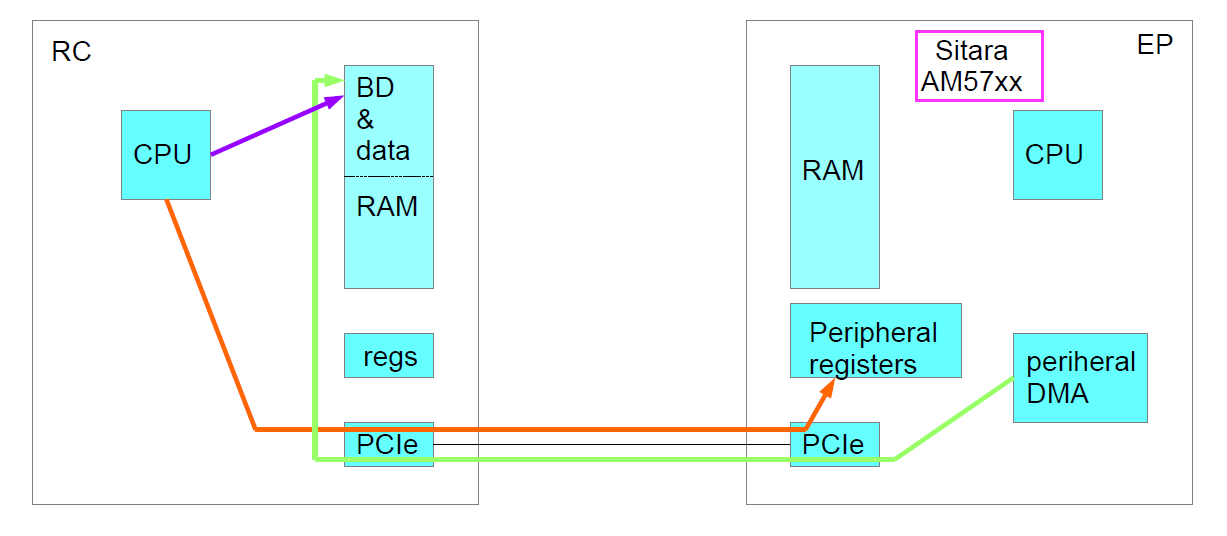

The system would like the below:

-AM57x CPU will be used just for the EP config and interrupt management.

Q: Can the AM57x (as PCIe EP) do DMA access (read/write) the RC RAM directly over PCIe (see green arrow)?

-Is it supported by the PCIe EP driver directly?

Q: Can the Host RC access (read/write) the different AM57x peripherals registers (like USB, Ethernet) over PCIe (see orange arrow)?

Q: According to the TRM SPRUHZ7G pg 6124 section 24.9.4.2, PCIe inbound read/write access is provided to the L3_MAIN, Can the peripherals on L4_PERx (see TRM page 377) be accessed via this mechanism through L3_MAIN?

Q:Can the DMA controllers used for USB and Ethernet peripherals access the 256 MiB PCIe outbound address space (See TRM pg 6126 section 24.9.4.3.2)?

Q: Can there be some hang-up situation when the PCIe interface is interrupted on the RC or EP side? Is this automatically managed by the PCIe HW? Should this be handled in the RC and EP driver?

Q: Regarding PCIe Linux driver benchmarks and performance:

What does the "PCIe-ETH" performance test refer to? Is there a description on the test case?

http://processors.wiki.ti.com/index.php/Processor_SDK_Linux_Kernel_Performance_Guide#PCIe_DriverDo we have additional performance figures available?

I have seen the below post that mention some performance but it does not seem to be performed on each Linux driver release:

https://e2e.ti.com/support/arm/sitara_arm/f/791/p/591681/2174826

Thanks in advance,

Anthony