Part Number: PROCESSOR-SDK-AMIC110

Other Parts Discussed in Thread: AMIC110, TIDEP-0105, , AM4377

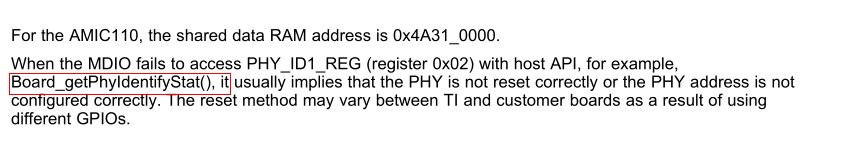

Hello,we are developing EtherCAT with Amic110(DDRless), we have be confused with compile EtherCAT pru;

a)In your document ,Tidep-0105;

you metioned:

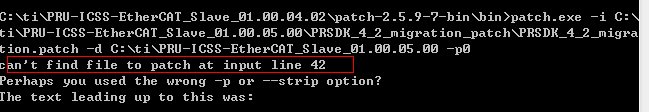

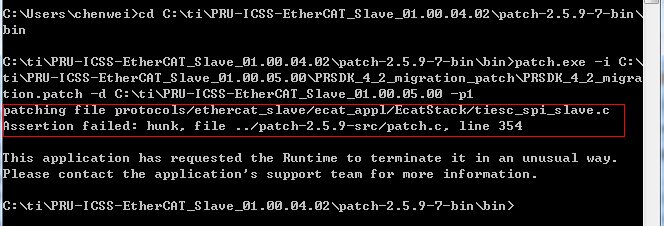

Currently, the SBL

(MLO) for DDR-less mode must be built from Processor SDK v4.2, with this patch. The patch is not

required for Processor SDK RTOS v4.3 and later.

It means we could use only sdk v4.2 to use ddrless mode?

b)the sdk v4.2 generates pdk v1.0.9;but in the document it also notes as bellows;

A patch file is included in the PRU-ICSS-ETHERCAT-

SLAVE v1.00.05 package at [INSTALL-

DIR]/protocols/pdk_patches/04.01.00/AM335x_PDK_1_0_8_thumb_mode.patch

Can the file AM335x_PDK_1_0_8_thumb_mode be used with pdk1.0.9?

c)Because the ethercat package and pdk package are changing with time, we do not known which vertion matches;

And in EtherCAT stack 1.0.5's user guider ,it metion about pdk,Processor SDK RTOS for AM335x 4.1.0:

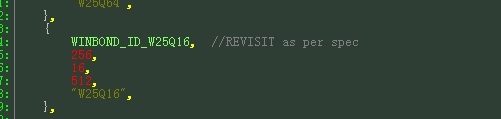

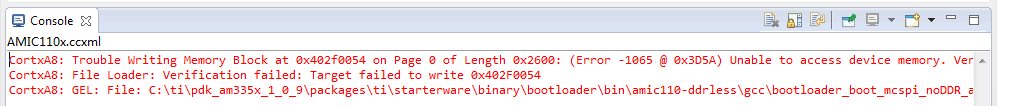

We use pdk1.0.9 (with EtherCAT stack 1.0.5')to build ethercat full demo, it reports strange errors;as we tried ,unmatched vertions lead to strange errors;

d)CAN you provide a file with every stack or file matched to ensure a correct Project;And Your document now are not explicit to us.

or CAN you provide a ddrless project which i only need to compile it and we can use it,we do not even need to download pdk or patch file;It is possible because we have tried in

other project.Other company's mcu is more easy to use(for example stm32).