Hello Champs,

1. Customer connected C6678 SRIO to FPGA (single lane).

1. Customer connected C6678 SRIO to FPGA (single lane).

2. He successfully used loopback mode to configure the LSU maintenance to access the DSP's CAR/CSR (HOP=1).

3. Then connecting to FPGA, the DSP, FPGA port initialization is OK, DSP (LANE3) register is ok ()(0x029001B8=0x00000002)

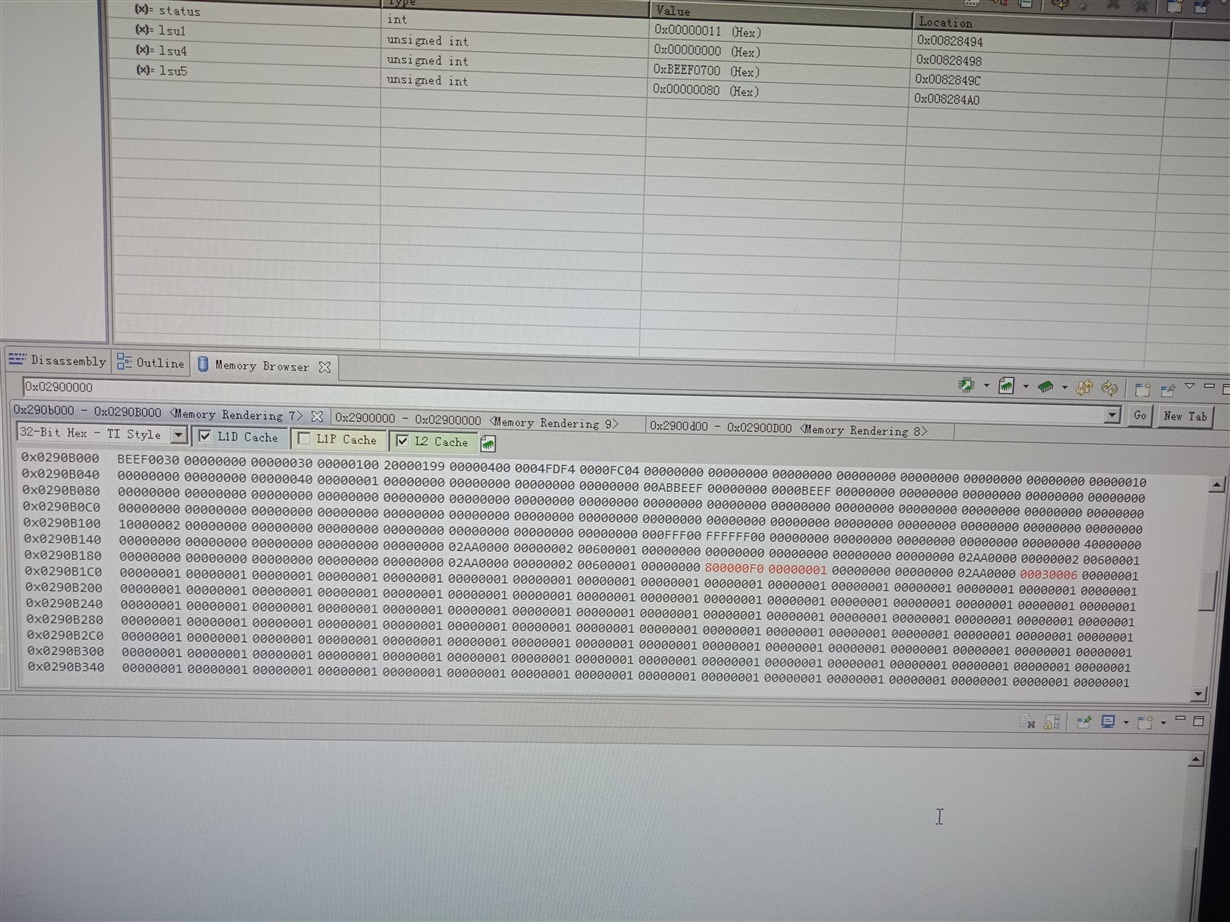

4. But when configurating LSU Maintenance, accessing both FPGA and DSP can cause Lsu_Stat的0b001( — Transaction Timeout occurred on Non-posted transaction), the CAR/CSR register are below:

Thanks.

Rgds

Shine

Rgds

Shine