rt Number: 66AK2G12

Tool/software: Code Composer Studio

Dear Sir,

Currently, We develop our product using 66AK2G12, And debug the DDR3.

So we are trying to our firmware load to DDR3 directly via JTAG and CCS.

But there is some problem happen.

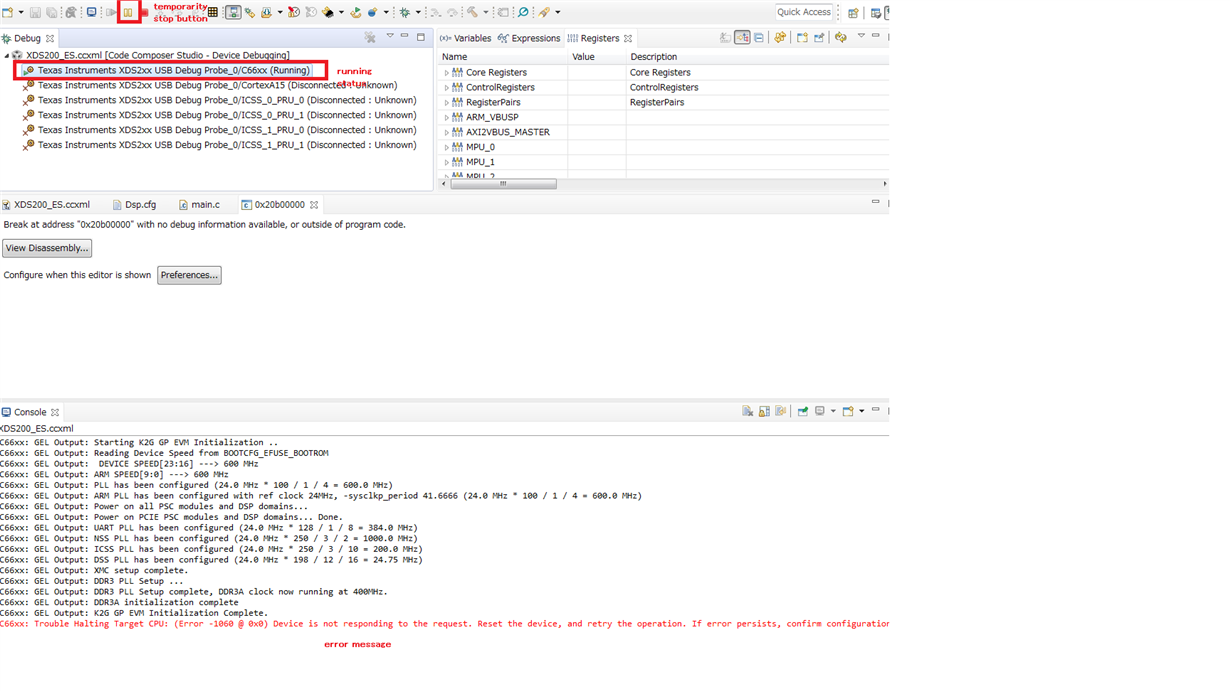

The error comment display on CCS. Please check attached file

(Below is error comment).

C66xx: File Loader: Verification failed: Values at address 0x81320568 do not match Please verify target memory and memory map.

C66xx: GEL: File: D:\test.out: a data verification error occurred, file load failed.

If we change the object attrs from "r--" to "rw-" ,This problem did not happen.

So we confirmed whether this phenomenon occurs when the attributes of the object are changed.(from "r--" to "rw-" / from "r--" to "rw-")

In the end,we noticed that this phenomenon occurs the "r--" object.

Please tell us the reason why is this phenomenon happen and what should we investigate. we have already finished the DDR3 read and write hardware check.