Other Parts Discussed in Thread: UCD9222, UCD7242

Tool/software: Code Composer Studio

hi all:

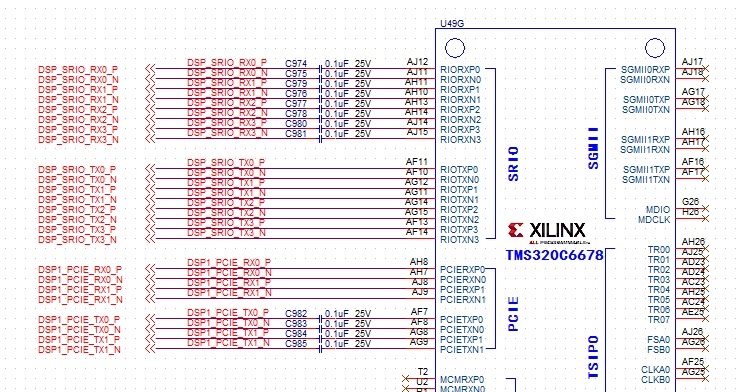

I have designed a custom board(board A), with two FPGAs: 7K325T and 7V690T, also with one DSP: TMS320C6678.

Now the power supplys and clocks for DSP is controlled by 7K325T, with the programmed bit, the DSP is initialized successfully.

All interfaces without SRIO(between 7V690T and C6678) word ok, include PCIE,SPI, I2C,EMIF (GE and Hyperlink is not used, so not connect).

The SRIO interface between 7K325T and 7V690T is ok, so I think the circuit of 7V690T is OK.

I try to initialise c6678 with 4 x1 1.25G interface, link can also not set up.

I have checked the electric circuit, nothing found.

I have another custom board(board B) with two 7V415T and two TMS320C6678, also with SRIO between FPGA and DSP. The srio interface test codes of DSP is ok on this board , so I thinks the codes is OK.

The differences between two custom board is as follow:

1)board A is TMS320C6678ACYP, and board B is TMS320C6678ACYPA;

2) Board A uses UCD9222+UCD7242 to supply CVDD and CVDD1, other powers are powered by LTM4644.

Board B use UCD9222+UCD7242 to supply CVDD of two DSPs, other powers are powered by LTM4644.

3) Board B use GE and Hyperlink interface, so corresponding pins are connected.

Can you give me some advise for this question?

Thanks.

Best wishes!