Other Parts Discussed in Thread: SYSBIOS

Hello ,

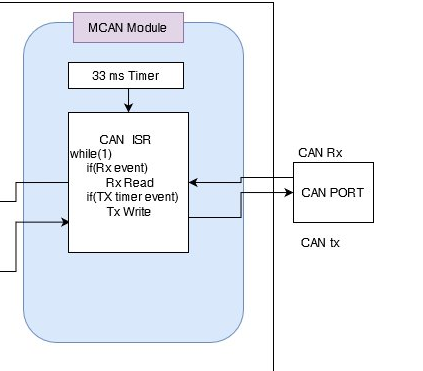

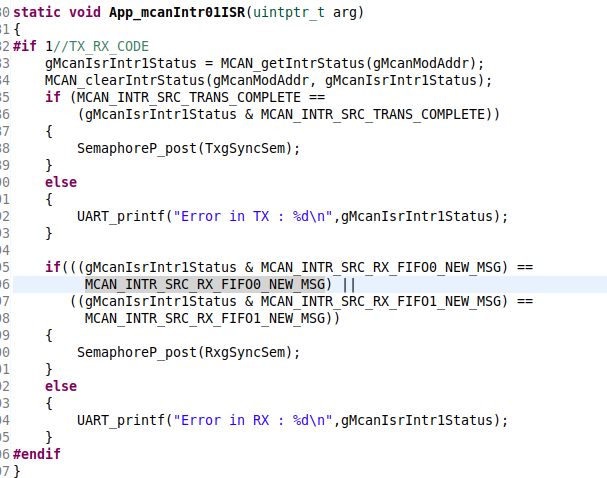

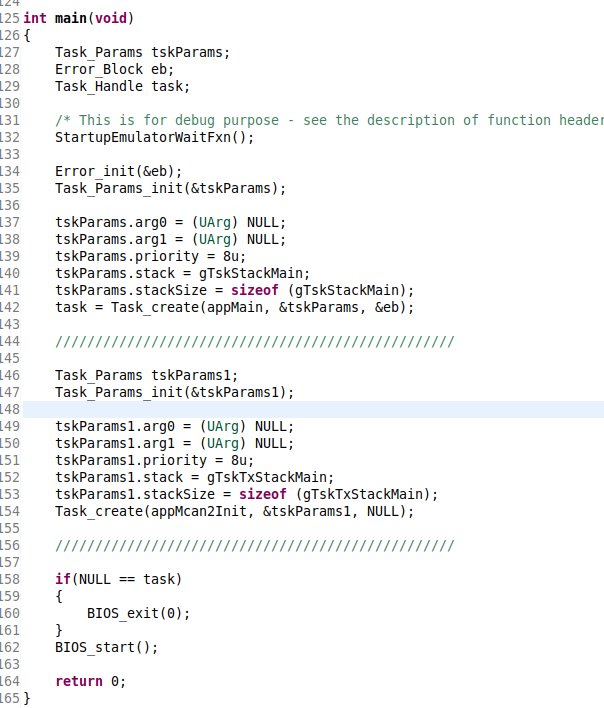

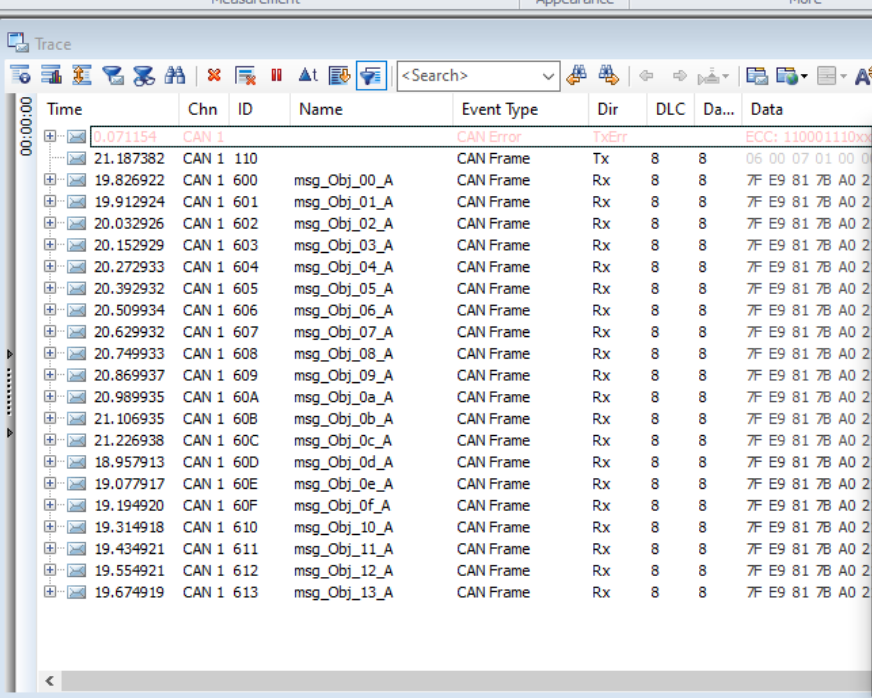

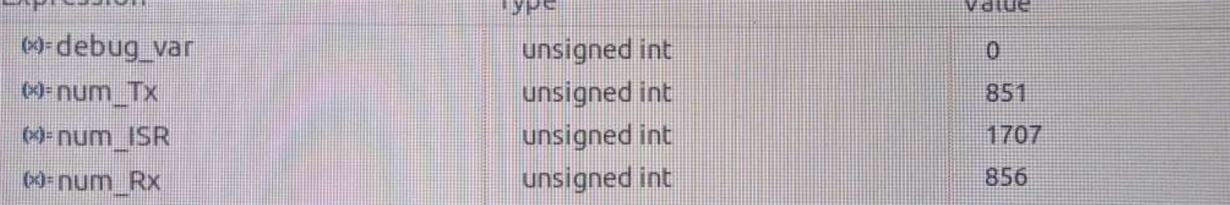

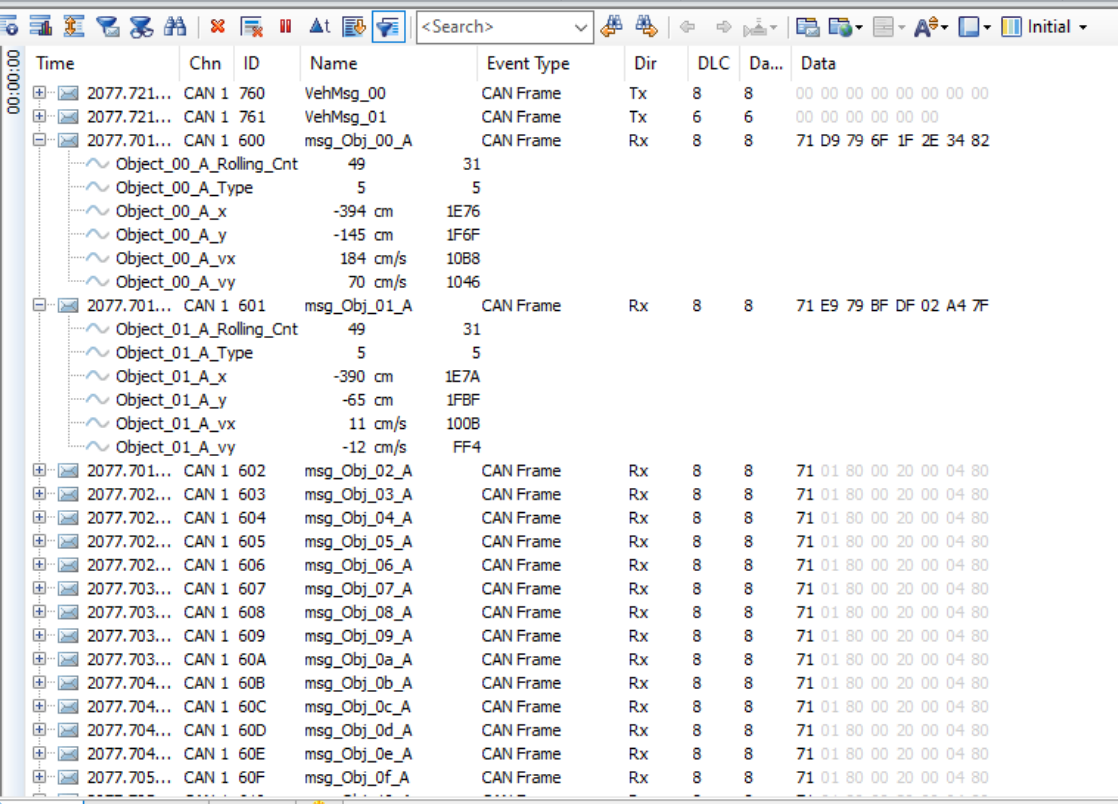

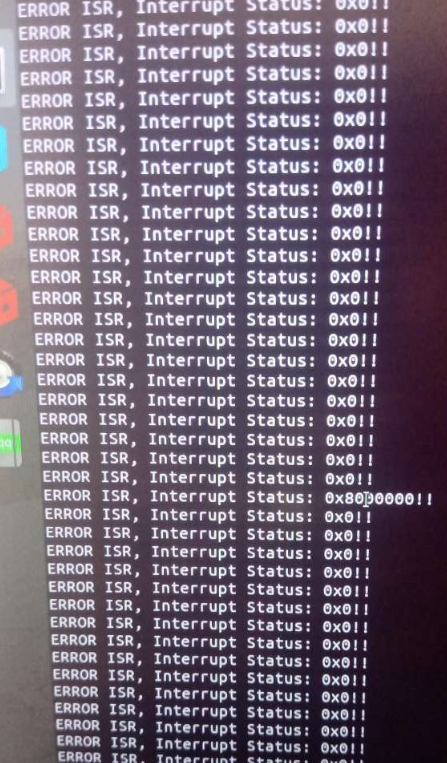

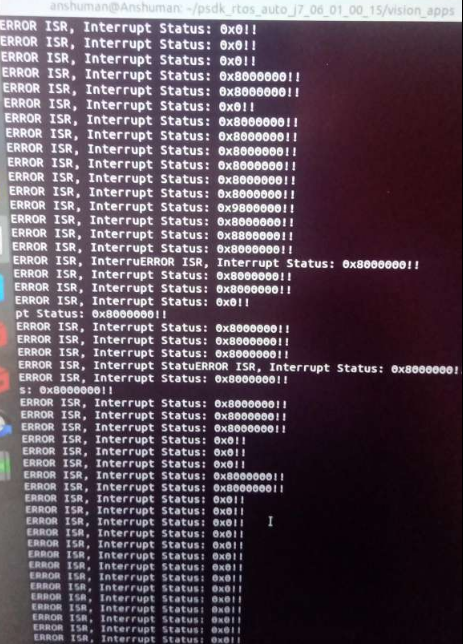

1. Currently we are working on camera based dl demo application.Able to asynchronously perform using MCAN2 either transmission or reception of messages by triggering the appMcan2Init() in appInit() [basic_demos/app_tirtos/common/app_init.c]

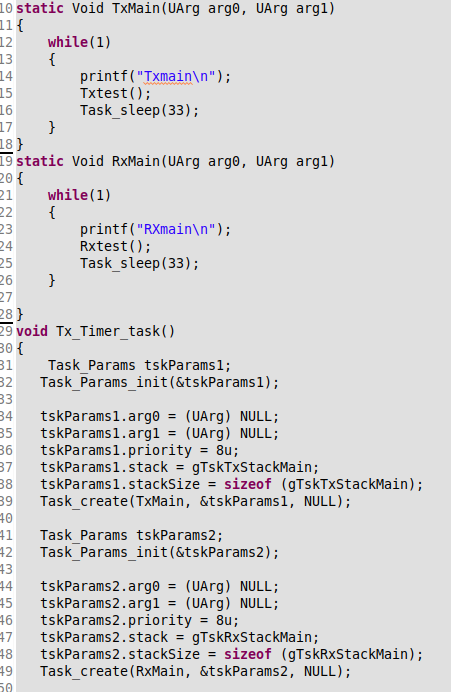

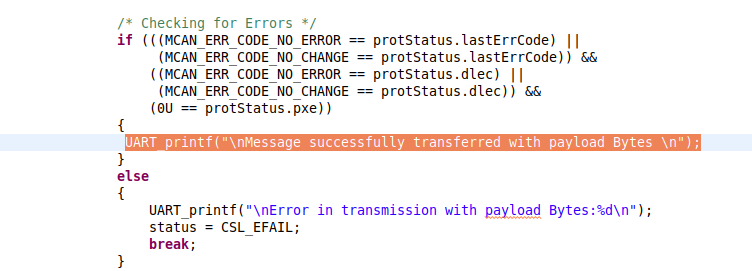

2. Now Tx of messages is happening after every 33ms using Task_sleep()

//pseudo code of Tx

while(1){

Txtest();

Task_sleep(timePeriodInMilliSec);}

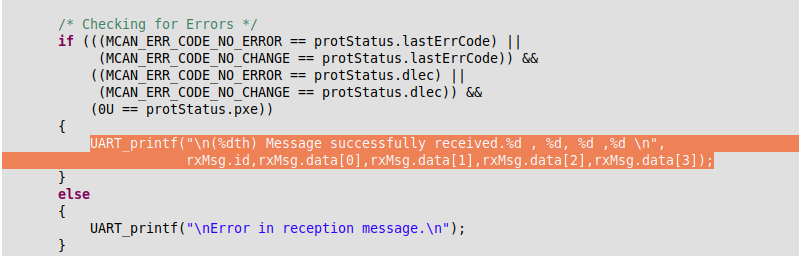

3. Rx is also receiving messages continuously.

//pseudo code of Rx

while(1){

Rxtest();}

4. Our final objective is to allow Tx to happen after every 33ms once dl demo application completes each frame (~33ms) and also continuously receive messages.

Kindly provide some guidance on this.

Thanks and Regards

Pooja Krishna