Part Number: DRA829V

Hi,

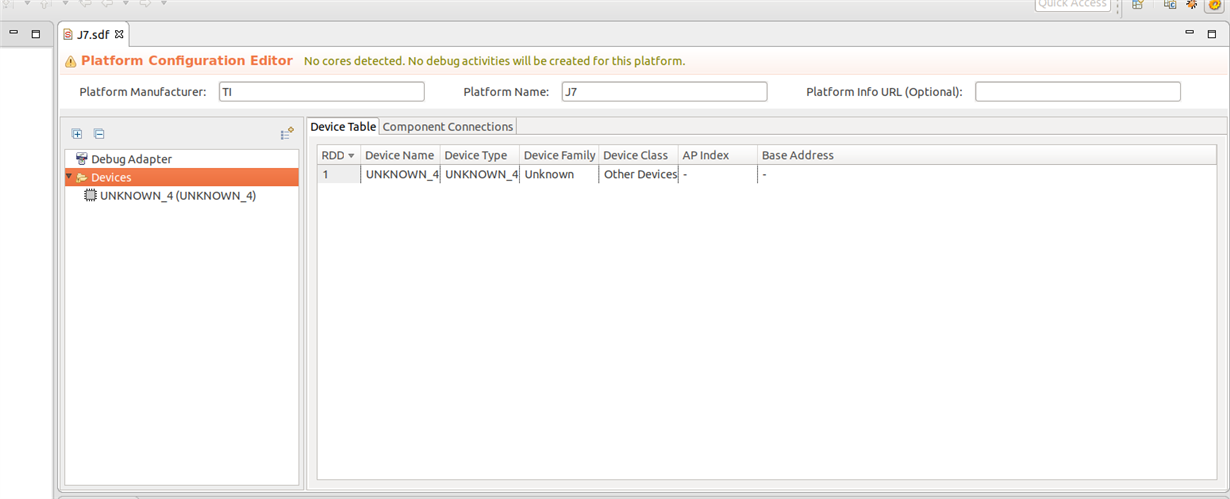

I am using J7 EVM target and I want to use an external JTAG probe (ARM DStream).

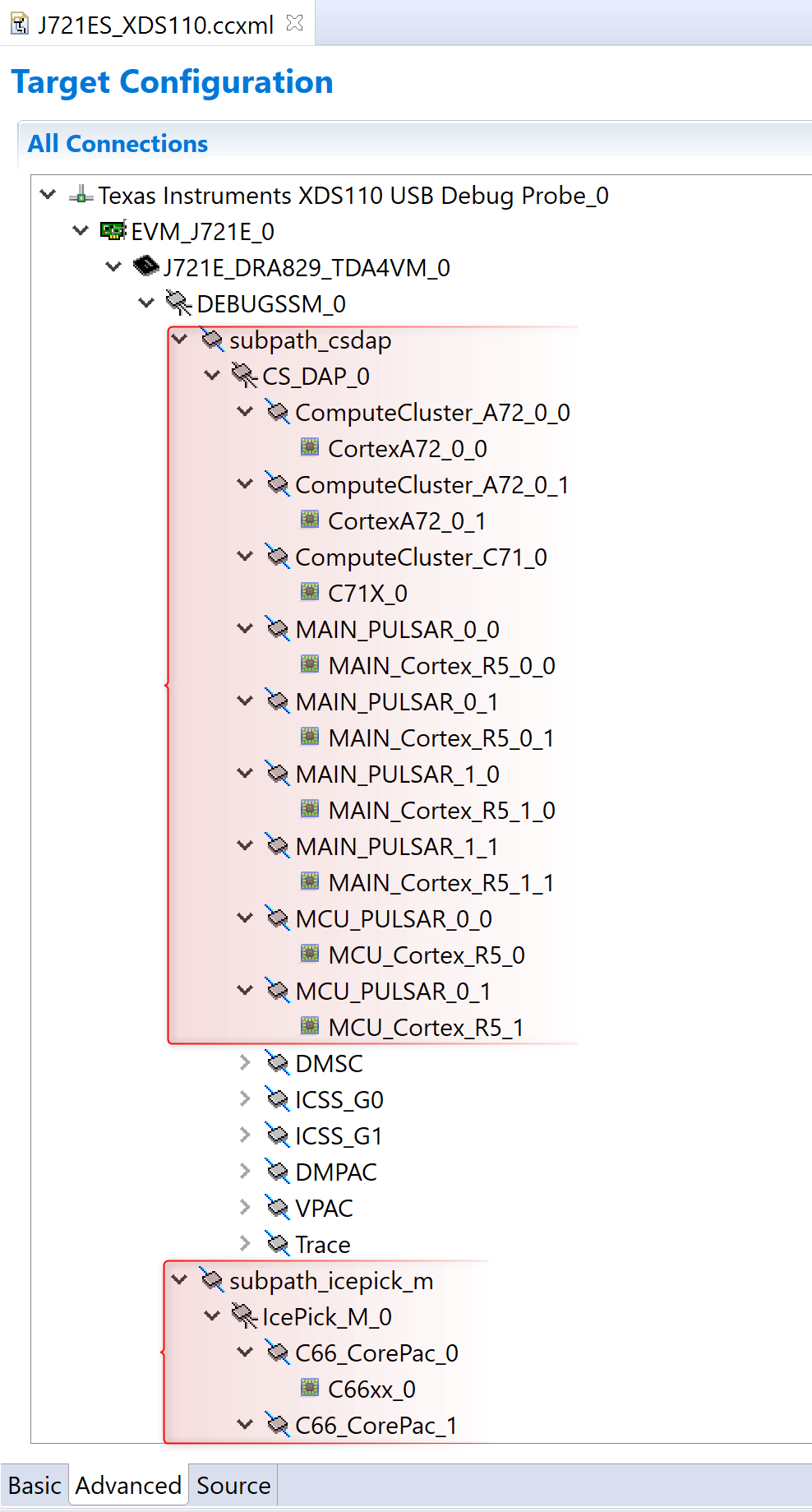

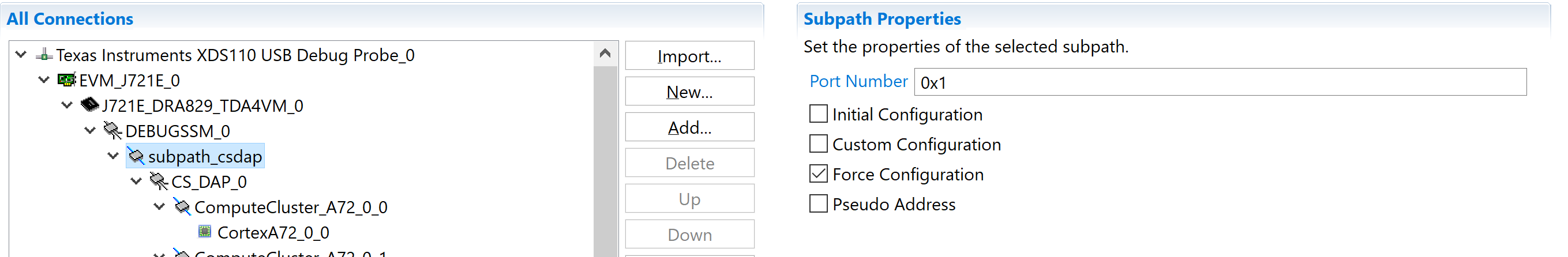

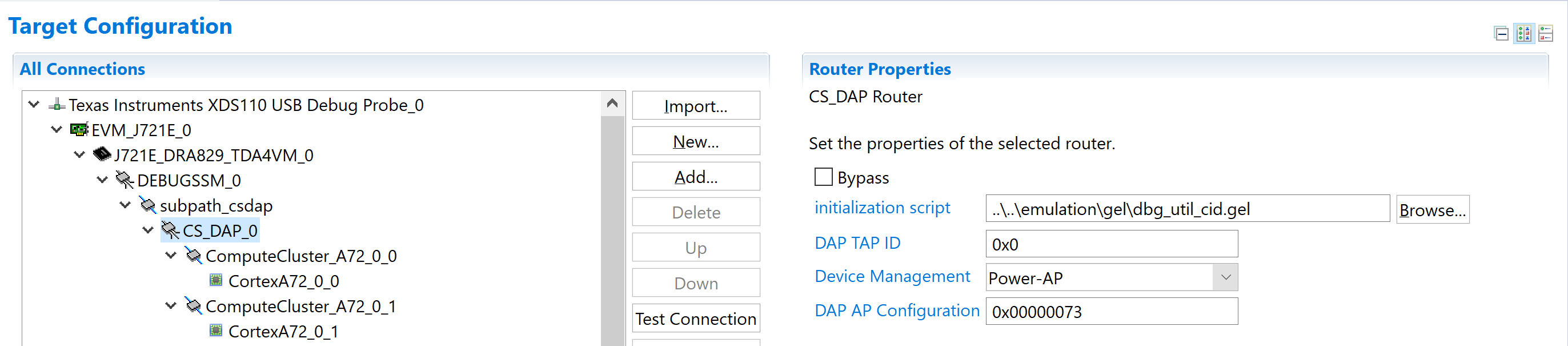

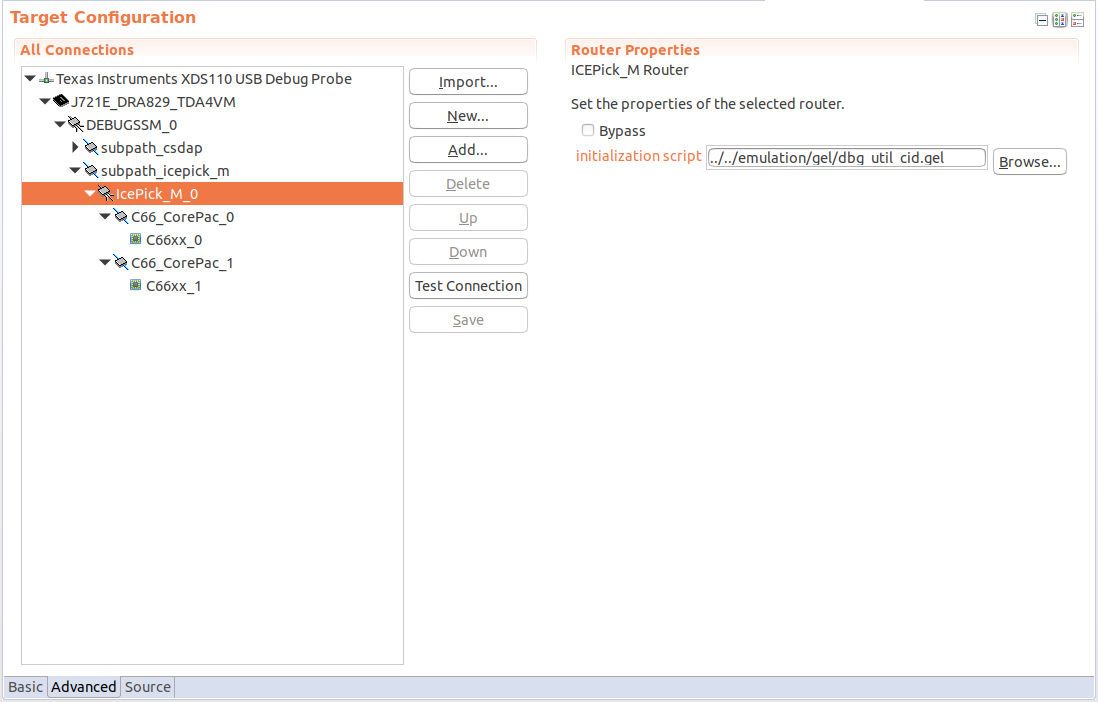

When I make a connection with the on-chip debugger XDS110, the Target Configuration in CCS suggests that my target has ICEPick-M router on it.

I used 'Autodetect Platform' of Arm DS-5 but did not succeed in the automatic detection of the scan-chain because I first need to program/configure the ICEPick router. There is information available about scan sequence for ICEPick-C and ICEPick-D https://processors.wiki.ti.com/index.php/ICEPICK?keyMatch=ICEPick-C&tisearch=Search-EN-Everything#What_is_ICEPick.3F but I couldn't find any information for ICEPick-M. Please provide me with the complete information for ICEPick-M.

Regards,

Iqra