Other Parts Discussed in Thread: TMDXEVMPCI

Hi,

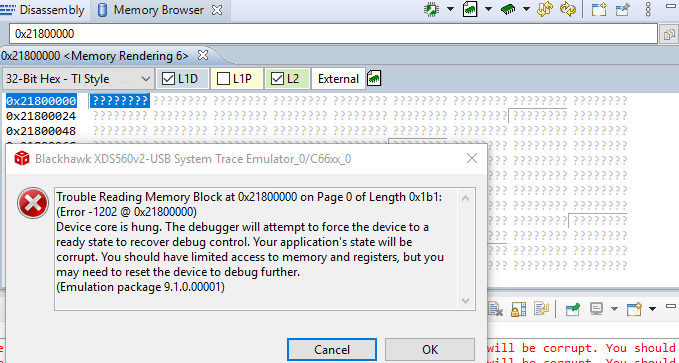

We are having trouble running run_dmatest.sh on CentOS 7 having TMDSEVM6678 & TMDXEVMPCI. cmem_dev kernel module's cmem_ioctl() is modified to use copy_from_user & copy_to_user (otherwise it crashes the kernel).

mmap seems succeed:

7f5c1b34b000-7f5c1b3cb000 rw-s d1400000 00:12 17344 /sys/devices/pci0000:00/0000:00:1d.0/0000:04:00.0/resource1

Debug: do_dsp_dma: dmaqnum_addr: 0x7f5c1b34b240

if(!(flag & FLAG_XFER_NOT_WAIT_TILL_COMPLETION)) {

do

{

usleep(1);

tmp = *((volatile uint32_t *) (mem_region_base + IPR));

} while(!(tmp & (1 << dma_chan_num)));