Other Parts Discussed in Thread: TDA4VM

Hi,

I've seen can0 and can1 in terminal by ifconfig -a with the method you supplied(https://e2e.ti.com/support/processors/f/791/t/922168) and can set can0/can1 up. Thanks!

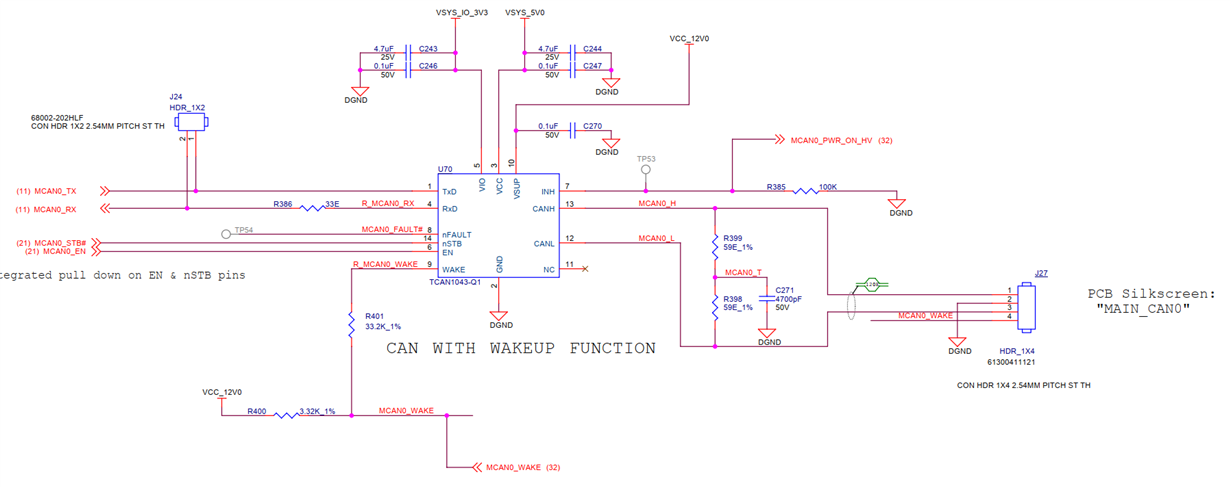

However, i meets another problem: when i execute "cansend can0 113##2AAAAAAAA", then returned info "m_can_platform 2701000.mcan can0: bus-off".

The changes are as follows:

diff --git a/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts b/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts index 6788a3611..b223fc97d 100644 --- a/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts +++ b/arch/arm64/boot/dts/ti/k3-j721e-common-proc-board.dts @@ -164,6 +164,21 @@ }; &main_pmx0 { + + mcan0_gpio_pins_default: mcan0_gpio_pins_default { + pinctrl-single,pins = < + J721E_IOPAD(0x0208, PIN_INPUT, 0) /* (W5) MCAN0_RX:GPIO1_1 */ + J721E_IOPAD(0x020c, PIN_OUTPUT, 0) /* (W6) MCAN0_TX:GPIO1_2 */ + >; + }; + + mcan2_gpio_pins_default: mcan2_gpio_pins_default { + pinctrl-single,pins = < + J721E_IOPAD(0x01f0, PIN_INPUT, 3) /* (AC2) MCAN2_RX.GPIO0_123 */ + J721E_IOPAD(0x01f4, PIN_OUTPUT, 3) /* (AB1) MCAN2_TX.GPIO0_124 */ + >; + }; + sw10_button_pins_default: sw10_button_pins_default { pinctrl-single,pins = < J721E_IOPAD(0x0, PIN_INPUT, 7) /* (AC18) EXTINTn.GPIO0_0 */ @@ -180,6 +195,37 @@ pinctrl-single,pins = < J721E_IOPAD(0x230, PIN_INPUT, 7) /* (U2) ECAP0_IN_APWM_OUT.GPIO1_11 */ >; + p06 { + /* P06 - MCAN0_EN */ + gpio-hog; + gpios = <6 GPIO_ACTIVE_HIGH>; + output-high; + line-name = "MCAN0_EN"; + }; + + p07 { + /* P07 - MCAN0_STB# */ + gpio-hog; + gpios = <7 GPIO_ACTIVE_HIGH>; + output-high; + line-name = "MCAN0_STB#"; + }; + + p13 { + /* P13 - MLB_MUX_SEL */ + gpio-hog; + gpios = <11 GPIO_ACTIVE_HIGH>; + output-low; + line-name = "MLB_MUX_SEL"; + }; + + p14 { + /* P14 - MCAN_MUX_SEL */ + gpio-hog; + gpios = <12 GPIO_ACTIVE_HIGH>; + output-low; + line-name = "MCAN_MUX_SEL"; + }; }; main_i2c0_pins_default: main-i2c0-pins-default { @@ -350,6 +396,15 @@ status = "disabled"; }; +&main_gpio0 { + p127 { + gpio-hog; + gpios = <127 GPIO_ACTIVE_HIGH>; + output-low; + line-name = "MCAN2_STB"; + }; +}; + &main_gpio2 { status = "disabled"; }; diff --git a/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi b/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi index c036df124..e5d84e44d 100644 --- a/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi +++ b/arch/arm64/boot/dts/ti/k3-j721e-main.dtsi @@ -1148,6 +1148,34 @@ clock-names = "gpio"; }; + m_can0: mcan@2701000 { + compatible = "bosch,m_can"; + reg = <0x0 0x2701000 0x0 0x200>, + <0x0 0x2708000 0x0 0x8000>; + reg-names = "m_can", "message_ram"; + power-domains = <&k3_pds 156 TI_SCI_PD_EXCLUSIVE>; + clocks = <&k3_clks 156 1>, <&k3_clks 156 0>; + clock-names = "cclk", "hclk"; + interrupts = <GIC_SPI 124 IRQ_TYPE_LEVEL_HIGH>, + <GIC_SPI 125 IRQ_TYPE_LEVEL_HIGH>; + interrupt-names = "int0", "int1"; + bosch,mram-cfg = <0x0 0 0 32 0 0 1 1>; + }; + + m_can2: mcan@2721000 { + compatible = "bosch,m_can"; + reg = <0x0 0x2721000 0x0 0x200>, + <0x0 0x2728000 0x0 0x8000>; + reg-names = "m_can", "message_ram"; + power-domains = <&k3_pds 160 TI_SCI_PD_EXCLUSIVE>; + clocks = <&k3_clks 160 1>, <&k3_clks 160 0>; + clock-names = "cclk", "hclk"; + interrupts = <GIC_SPI 130 IRQ_TYPE_LEVEL_HIGH>, + <GIC_SPI 131 IRQ_TYPE_LEVEL_HIGH>; + interrupt-names = "int0", "int1"; + bosch,mram-cfg = <0x0 0 0 32 0 0 1 1>; + }; + main_gpio2: gpio@610000 { compatible = "ti,j721e-gpio", "ti,keystone-gpio"; reg = <0x0 0x00610000 0x0 0x100>; -- 2.17.1

Regards