Other Parts Discussed in Thread: AM623, AM2434, TDA4VM, AM6548, AM2431, AM62P5-Q1, AM62A3-Q1, TDA4AL-Q1, TDA4VM-Q1, TDA4AH-Q1, MCU-PLUS-SDK-AM243X, SK-AM62A-LP, AM62A7, TDA4VH-Q1, AM3358, SEGGER, AM62P, AM62L, TMS320C6416, TMS320C6416T, AM62A7-Q1, AM62D-Q1, OMAP-L138

Tool/software:

Hi TI Experts,

I have the below queries regarding the use of JTAG interface

JTAG connection recommendations

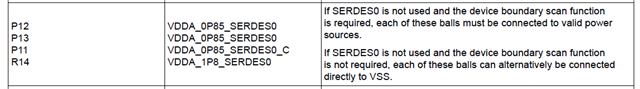

Connections to support Boundary scan

JTAG connectors

Let me know your thoughts.