Tool/software:

Hi David,

This is in the response to the following locked thread: https://e2e.ti.com/support/rf-microwave-group/rf-microwave/f/rf-microwave-forum/1427050/afe7950evm-afe7950-qpll0-is-not-getting-locked-when-configured-through-afe79xx-latte-gui .

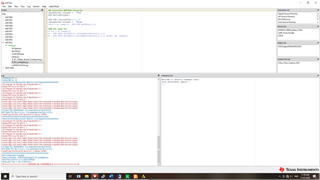

Apologies for the late reply. The "PLL2 Locked" LED is glowing; however, in chipscope, the qpll0_locked value does not change to 3 after deasserting master_reset_n. We have 2 key concerns; firstly, we want to confirm whether the glowing LED definitively indicates that PLL2 is locked, or could there still be an issue causing the problem in chipscope despite the LED being on? Additionally, since we are using the default script and provided files, are there any specific parameters we should check or modify to resolve this? Thank you for your assistance.