Hi team,

I have an application question which need your help.

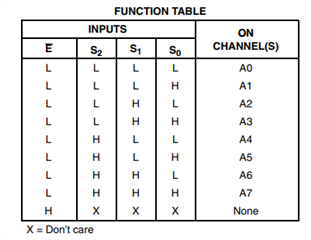

After the chip is powered on, what is the state of S0 S1 and S2? Does X mean high impedance? And if not, what would it be?

If the GPIO pin of C2000, which connected to S0 is set to input mode during use, what will be the impact?

Looking forward to your reply~