Other Parts Discussed in Thread: CONTROLSUITE, C2000WARE

Tool/software: Code Composer Studio

Hello,

Recently I've been working on a project on F28069M microcontroller mounted on Launchpad_XL, now I'm almost finished with the project and I wanted to Flash the whole code inside the microcontroller, and that was the moment that I realized I'm facing a super complicated issue! (at least what I see in forums and documentations and after 20 hours of working on the issue and finding almost no solution).

Let's start with the problem:

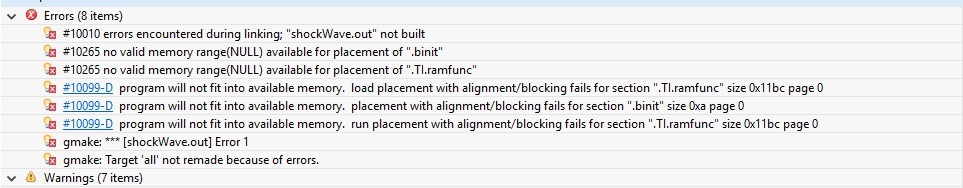

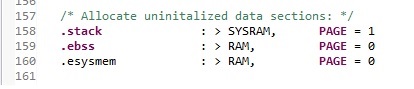

I wrote an application which keeps the current fixed across some coils, I use PI controllers from DCL library and a lot of other features of F28069. When I run my code through debugger in RAM mode everything works fine and I can control the system. For moving the codes from RAM to flash ( or more technically speaking to loading codes from Flash to RAM in the beginning of the booting) I read "spra958l" and I took a look at the sample codes, but the problem I have is my code at some certain points gets stuck in Illegal ISR or when it goes to functions it can not return. ( I have modified the linker files based on the example code for Flashing in ControlSuit).

First of all I want to know how can I verify in code composer that I'm assigning right memory parts /functions to RAM or Flash memories ( SDFlash utility is recommended in one of the ControlSuit examples but it suffers from lack of documentations and is extremely complicated)

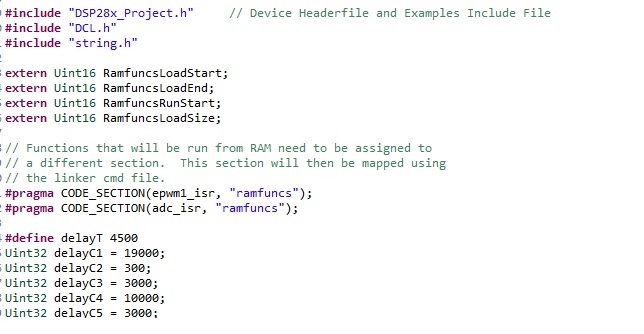

Secondly this is some parts of my code :

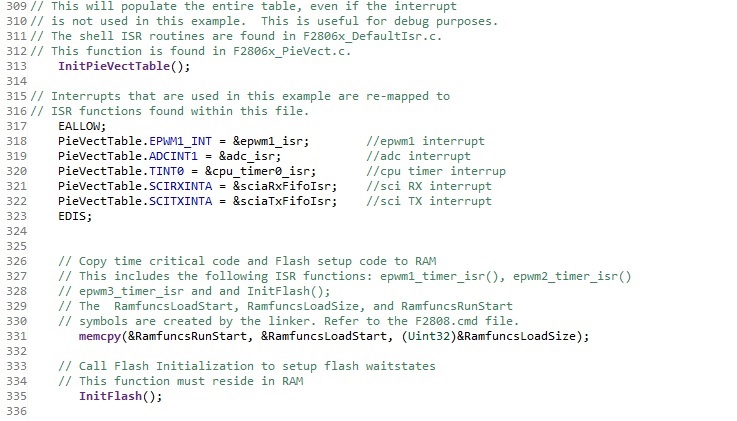

inside the main after some initialization of the clocks I have this part of code for copying memories:

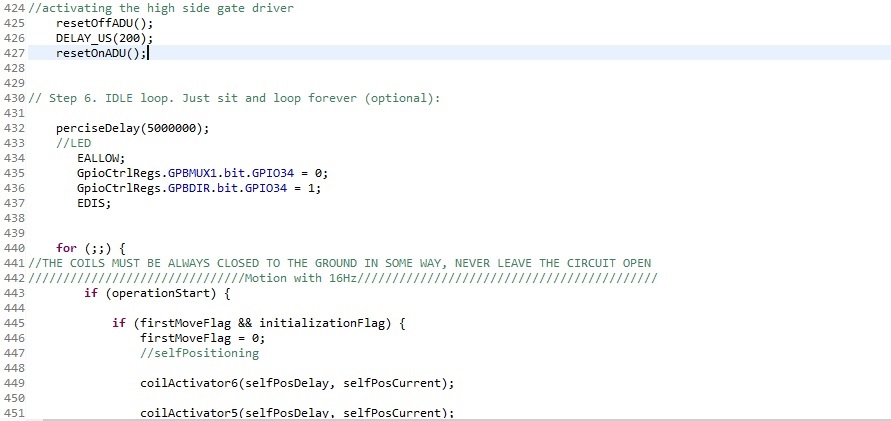

and the code reaches up to here:

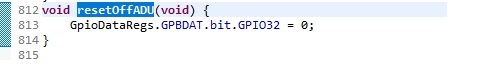

I can run the code up to "resetOffADU();" function and then the code goes in illegal ISR, when I comment this function, still inside the forever loop I again get stuck in other functions for timing and etc.

the "resetOffADU();" function is just a simple GPIO pin setting.

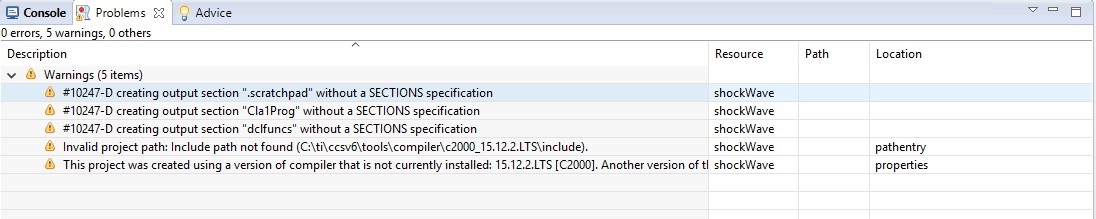

These are also some suspicious warnings which I'm receiving:

This is the first time that I face a problem in Texas microcontrollers which is such complicated and there aren't proper and solid documentations for that, I highly appreciate if you can lead me to the solution.