はじめに

この記事では、PSpice® for TIを使用して、モーター・ドライブ設計での寄生成分の潜在的な原因をシミュレートし、悪影響を軽減するための設計のヒントを提供します。

高電力システムの設計で最も厄介な部分の1つが、寄生成分による捉えどころのない結果です。これは特に、高電力のモーター・ドライブ・システムで問題となります。そのようなシステムでは、基板や部品のサイズが大きく、出力電流も大きいことで、出力のリンギングや過度の部品定格、または放射電磁干渉(EMI)につながる場合があるからです。

高電力のモーター・ドライブ設計とは

モーター・ドライブ・システムに深く関わっているエンジニアにとって、特定の課題に応じてモーター・ドライブ・システムを設計するのは基本的な方法です。高電力システムで寄生分析が重要であるのには、2つの明確な理由があります。

まず、高電力には高電流が伴うということです。モーターで1Aをスイッチングする場合の影響は、100Aをスイッチングする場合と同じではありません。高電流では、プリント基板(PCB)上の固有の寄生インダクタンスや寄生容量のすべてがすぐに問題を生み始めます。電流を低く保てるほど、これらの寄生成分の影響は小さくなります。ただし、定義された高出力電力を持つシステムでは、目標出力電流が固定されているため、浮遊インダクタンスや浮遊容量があると設計に大きく影響します。

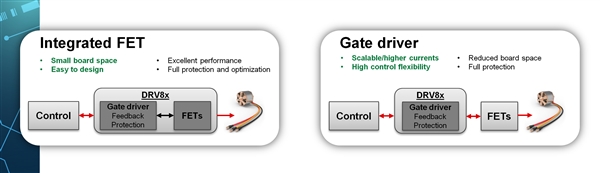

次に、高電力のモーター・ドライブ・システムにはゲート・ドライバ・アーキテクチャが必要です。モーター・ドライバには2つのタイプがあり、1つはFET(電界効果トランジスタ)内蔵型、もう1つはゲート・ドライバに外部FETを使用するタイプです(図1を参照)。FET内蔵モーター・ドライバは、低電力システムには非常に有効です。なぜなら、ゲート・ドライバ、電力段、その他のセンシングおよび保護を1つのパッケージに統合しているからです。また、これらのデバイスは非常に小さいため(例えば、『DRV8837C』はわずか2×2mm)、基板の寄生成分が大きく減少します。ただし残念ながら、最も高電流のFET内蔵ソリューション(例えば、『DRV8873-Q1』は最大10Aを駆動可能)でも100Aのモーターは駆動できないため、ゲート・ドライバ・アーキテクチャが必要になります。モーター・ドライバ・システムでゲート・ドライバとともに外部のディスクリートMOSFETを使用すると、常に基板上の部品間にプリント配線が存在するため、寄生成分が生じます。

図1:FET内蔵型とゲート・ドライバ型のアーキテクチャ

図1:FET内蔵型とゲート・ドライバ型のアーキテクチャ

ゲート・ドライバ回路と印加されるパルス

分析用の回路を作成するために、単純化されたハーフブリッジ・モーター・ドライバから開始します(図2)。この回路で使用したモーター・ドライバは、TIの『DRV8343-Q1』であり、これは電流シャント・アンプを搭載した3相スマート・ゲート・モーター・ドライバです。MOSFETはTIの『CSD18540Q5B』であり、選択したゲート駆動強度(IDRIVE)はソース15mAおよびシンク30mAです。単純化のために、1つの位相だけを使用して、モデル負荷(240mΩおよび50µH)を作成しました。ここで使用した電源は24Vです。

図2:単純化したドライバ回路(寄生要素なし)

次に、「パルス・テスト」をシミュレートしました。これは、ハイサイドMOSFETを所定の時間だけオンにしてから、パルス状にすばやくオフにしてオンに戻し、その間、回路に大きな電流が流れるというものです。パルス・テストのシミュレーションでは、ハイサイドMOSFETがオフになり再度オンになるときに、出力の立ち下がりエッジと立ち上がりエッジで生じる影響を観察することができます。図3は、印加される制御信号、ハイサイド・ゲートで期待される理想的な波形、および出力電圧を示しています。このシミュレーションでは、ハイサイドMOSFETを400µsにわたってオンにし、30µsの間パルスでオフにした後、残り70µsにわたってオンにしています。ローサイドMOSFETはオフに保持されるため、流れる電流はすべてローサイドMOSFETのボディ・ダイオード経由で導通します。

図3:パルス・テストの波形(寄生要素なし)

寄生成分の追加とシミュレーション

この回路に想定される寄生成分を追加すると、回路はすぐに複雑性を増し、回路図はもはや「良好」とは言えなくなります。これを行うには、重要な寄生成分を3か所に追加する必要があります。

- 電源とハイサイドMOSFETの間(HS)

- グランドとローサイドMOSFETの間(LS)

- ハイサイドMOSFETとローサイドMOSFETの間(PHASE)

この3つの場所は、一般にPCB上に非常に大きな配線パターンが見られる箇所で、大電流の流れる経路に相当します。図4をご覧ください。

図4:寄生要素のあるドライバ回路

寄生要素には以下を使用しました。

- ハイサイド(HS):10nF、5nH/10mΩ

- 位相(PHASE):2nF、2nH/2mΩ(パスごと)(負荷への出力に10nFを追加)

- ローサイド(LS):10nF、5nH/10mΩ

これは単にシミュレーションなので、潜在的に誇張した寄生インダクタンスと寄生容量を使用しました。軽減のプロセスは同じですが、これらの寄生成分を最小限に抑えるよう基板を設計して、軽減を容易にすることも可能です。反対に、設計の良くないPCBでは寄生インダクタンスと寄生容量がさらにずっと大きくなる場合もあり、その場合は寄生成分の軽減もずっと難しくなります。モーター・ドライバのレイアウト手法の確認には、アプリケーション・ノート『モーター・ドライバの基板レイアウトのベスト・プラクティス(英語)』をお勧めします。

これらの寄生成分を追加する前(図2)と追加した後(図4)に回路をシミュレートすると、回路を壊してしまったのではないかと思うほど大きな差が生じました。図5では、ハイまたはローへのスイッチング時に位相(PHASE)で発生する大きな発振が示されています。これらの影響を軽減して、回路を損傷(–20Vの負電圧スパイクなど)から保護したり、望ましくない電磁放射(発振の生じる配線がアンテナとして機能)を防ぐことが重要です。

図5:寄生成分を追加する前と後のPSpice for TIシミュレーションの結果

最適な軽減対策を検討するために、異なる寄生成分を1つずつ調べ、それぞれの影響をシミュレートしましょう。

電源とハイサイドMOSFETの間の寄生成分(HS)

電源とハイサイドMOSFETの間に寄生成分を追加すると(図6)、シミュレーションでは立ち上がりエッジの出力で非常にはっきりした発振が示されました(図7)。より詳しく調べると、この発振がハイサイドMOSFETのドレイン(VDRAIN)から来ていることがわかります。ハイサイドMOSFETをオフにしたときの立ち下がりエッジでも、この同じ影響が見られますが、出力には影響が及びません。

図6:ハイサイド・パス(HS)に寄生成分を追加したドライバ回路

図7:ハイサイド・パス(HS)に寄生成分を追加した立ち上がりエッジのシミュレーション

この段階では、スナバを追加する必要がある、またはスルーレートが高すぎるので下げる必要があると思われるかもしれません。ですが、スナバが最も効果的なのは、PHASEの発振の低減にであって、VDRAINの発振にではありません。調査のために、ハイサイドとローサイドの両方のMOSFETに1.2Ωと33nFのスナバを実装してみました。この効果を図8に示します。ここでは、依然としてVDRAINがスイッチング前に降下しているので、これはリンギングの軽減に最適な方法とは言えません。

図8:VDRAINの発振であるため、スナバを使用しても軽減の効果は低い

スナバの設計について詳しくは、技術記事「Power Tips:7つのステップでR-Cスナバを計算する」を参照してください。

発振を低減するためのもう1つの解決策は、スルーレートを下げることです。シミュレーションではそれによってリンギングが大きく減少しますが、ゼロにはなりません(図9)。スルーレートを下げると、スイッチング損失が増えるために電力損失が増加(部品の温度が上昇)するので、できれば避ける必要があります。この例では、ゲート駆動電流を15mA(ソース)から1.5mA(ソース)へと下げ、立ち上がり時間を10倍長くしています。

図9:ゲート駆動電流を下げて立ち上がり時間を長くしても、

電力損失の増加と連続的な発振により、軽減の効果は低い

これらの影響をさらに軽減するために、VDRAINノード(図10)に大きなバルク容量を追加してみましょう。これにより、発振がずっと遅くなり、振幅も小さくなります。ここでは単純に、このインダクタとコンデンサの時定数を非常に長くしました。図11に、その結果を示します。シミュレーションでは、バルク・コンデンサの追加によって発振のピークが37V(電源を13V上回る)から、より管理しやすい25V(電源を1V上回る)へと低下しました。このコンデンサは、コンデンサとMOSFETの間に追加で生じる寄生インダクタンスを軽減するために、可能な限りハイサイドMOSFETに近づけて配置する必要があります。リード・インダクタンスが小さく、高周波応答が良いことから、セラミック・コンデンサが推奨されます。

図10:VDRAINにバルク・コンデンサを追加

図11:バルク・コンデンサ(VDRAIN–GND間)によってハイサイドの寄生成分を軽減

グランドとローサイドMOSFETの間の寄生成分(LS)

ローサイドのパスは、ハイサイドのパスとほぼ反対です。立ち下がりエッジで大きな発振が生じ、立ち上がりエッジはクリーンに見えます。詳しく調べると、立ち上がりエッジと立ち下がりエッジの両方で、ローサイドMOSFETのソース・ノード(SLA)にリンギングが生じているのがわかります(図12)。

図12:ローサイド・パス(LS)に寄生成分を追加した回路図とシミュレーション

このような状況では、スナバを追加したり、立ち上がりエッジを長くしたりすることでリンギングに対処したくなるかもしれませんが、ここでもやはり、そのようなアプローチは避けるべきです。前と同様に、ハイサイドとローサイドの両方のMOSFETに1.2Ωと33nFのスナバを実装しました。結果として位相(PHASE)の発振は劇的に改善されましたが、最初の負電圧パルスは残っています(図13)。

図13:負電圧スパイクがあるため、スナバを使用しても軽減の効果は低い

スルーレートを下げると、リンギングは大きく減少します(図14)。この例では、ゲート駆動電流が30mA(シンク)から7mA(シンク)へと下がり、立ち下がり時間は4倍以上になっています。

図14:ゲート駆動電流を下げて立ち下がり時間を長くしても、電力損失の増加により、軽減の効果は低い

ハイサイドの場合と同様なアプローチを採用して、基板にバルク容量を追加することで、このリンギングに対処することが可能です。ただし、その場合、SLAとグランドの間に大きなコンデンサを追加するのは望ましくありません。ほとんどのモーター・ドライブ・システムでは、電流センス抵抗と電流センス・アンプを使用してローサイドに電流センシングを実装しています。一般的な2512パッケージのセンス抵抗には、1~5nHの寄生インダクタンスがあり、ここで仮定した寄生値が適切であることがわかります。

センス抵抗と並列に非常に大きなコンデンサを接続すると、システムが電流を正しく検知する能力が損なわれます(図15)。このバルク・コンデンサを追加する正しい場所は、VDRAINとローサイド・ソース(SLA)との間です。このデカップリング・コンデンサを追加する際には、センス抵抗を流れるピーク電流に多少の影響が残ることに注意してください。このコンデンサの値があまり大きすぎると、ローサイドの電流センシングによるピーク過電流制限に影響が及びます。

図15:ローサイドの寄生成分軽減のためのバルク・コンデンサの誤った配置(a)と正しい配置(b)

図16に、この追加の結果を示します。シミュレーションでは、バルク・コンデンサの追加によって発振のピークが–16Vから–3Vへと大きく低下しました。前の場合と同様に、このコンデンサはハイサイドMOSFETのドレインおよびローサイドMOSFETのソースにできる限り近づけて配置する必要があります。それによって、コンデンサと各MOSFETの間に追加で生じる寄生インダクタンスを軽減します。ここでもやはり、リード・インダクタンスが小さく、高周波応答が良いセラミック・コンデンサが推奨されます。

図16:バルク・コンデンサ(VDRAIN–SLA間)によってローサイドの寄生成分を軽減

MOSFET間の寄生成分(PHASE)

スイッチング時の寄生成分を最小限に抑えるために、ハイサイドMOSFETとローサイドMOSFETを互いになるべく近くに配置する必要があることはご存じかもしれません。しかし、これらの悪影響を完全になくすことはできません。最も効果的な複数ダイのMOSFETソリューション(例えば『CSD88599Q5DC』を参照)でも、ハイサイドMOSFETとローサイドMOSFETの間にいくらかの寄生インダクタンスと寄生容量が存在します。MOSFETの出力容量(COSS)とモーターのケーブル容量(ケーブル長が長い場合)は、PCB外部から見た位相ノードの容量に大きく寄与する可能性があります。

この場合、寄生インダクタンスをバイパスするために回路にバルク容量を追加することはできません。モーターへの出力はハイとローにスイッチングされ、この部分に大きなコンデンサが追加されると、これが繰り返し充放電されるため、非常に効率の悪いシステム・ソリューションとなります。このような状況では、最初の戦略としてスナバを使用するのが最善です(図17)。スナバ支持者の方々は安堵されることでしょう。ようやくスナバを使用します。回路にスナバを追加する効果は、図18に示されています。

図17:位相パス(PHASE)に寄生成分があり、スナバを追加した回路図

図18:スナバによるPHASEの寄生成分の軽減

スナバは立ち上がりエッジの発振をほぼ完全に解決し、立ち下がりエッジでも状況を大きく改善しています。前の実験と同様に、ハイサイドとローサイドの両方のMOSFETに1.2Ωと33nFのスナバを実装しました。ただし、ローサイドMOSFETの寄生成分の場合(図14)と同様に、最初の負パルスは残っています。

この段階では、これらの寄生成分を完全に解決するには立ち下がりエッジを長くする必要があると結論できます。『DRV8343-Q1』の絶対最大定格(–7V、200ns)内に収めるために、図18の立ち下がりエッジの–11Vの負電圧スパイクを改善する必要があります。ゲート駆動電流シンクを30mAから10mAに低減すると、負電圧スパイクが最大定格内に収まります(図19)。

図19:スナバとゲート駆動電流シンクの低減によるPHASEの寄生成分の軽減

まとめ

では、このシミュレーション演習から学んだことは何でしょうか。この3つの一般的な寄生成分(ハイサイド、ローサイド、位相)には、3つの異なる軽減手法があります。これらのすべての寄生成分が含まれる回路に、この記事で説明したすべての軽減手法を適用すれば(表1)、オーバーシュート、アンダーシュート、およびリンギングを大幅に削減できます(図20)。

表1:寄生成分の軽減手法のまとめ

図20:説明した手法を用いてすべての寄生成分を軽減

PSpice for TIシミュレーション・ツールは、物理的な基板の実験よりもずっとすばやく簡単に実行でき、基板の寄生成分に関する実世界の問題に直面したとき、優れた対処方法を示唆してくれます。

PSpice for TIの詳細については、技術記事「PSpice for TIを使用して複雑なアナログ電源および信号チェーン回路をシミュレーションする方法」と、ビデオ・トレーニング・シリーズ「PSpice for TIの概要(英語)」をご覧ください。TIのモーター・ドライバ、トレーニング、リソースの詳細については、こちらをご参照ください。

著者情報

Matt Hein (Texas Instruments)

※2021年4月30日 TECH+掲載のテキサス・インスツルメンツ寄稿記事を転載

※すべての登録商標および商標はそれぞれの所有者に帰属します。

※ご質問はE2E Support Forumにお願い致します。