Other Parts Discussed in Thread: TINA-TI, OPA171

Hi,

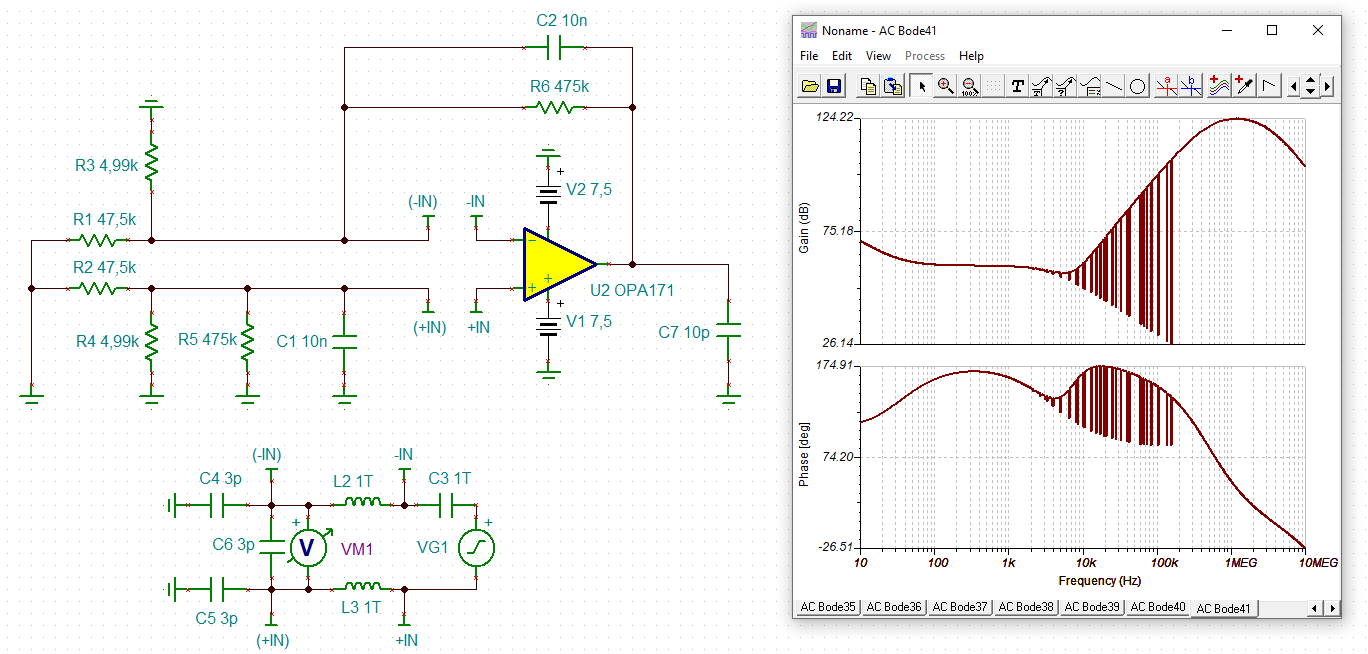

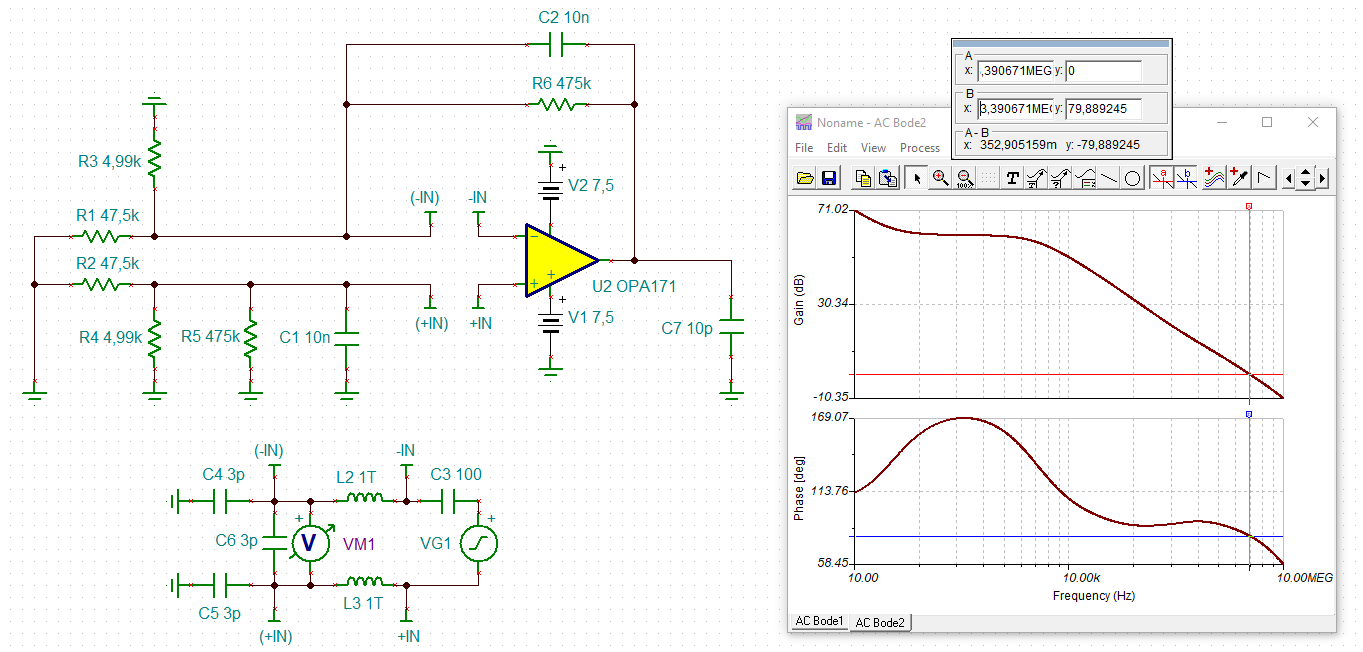

I have below circuit as a difference amplifier with the gain of 10. The circuit has feedback capacitor of 10pF. This is more like differential to single stage configuration and around 7.5V DC offset is provided at the input.

I have following questions:

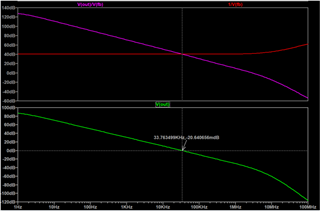

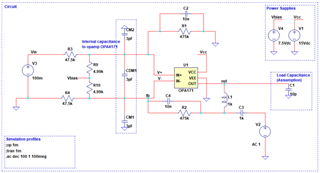

1. I am using the break the loop method (feedback loop) to understand the frequency response of the circuit. And added input capacitances to the simulation from datasheet of OPA4171.

As per one reference note: feedback capacitor > CCM + CDIFF, which is true in this case. I want to understand the role of feedback capacitor.

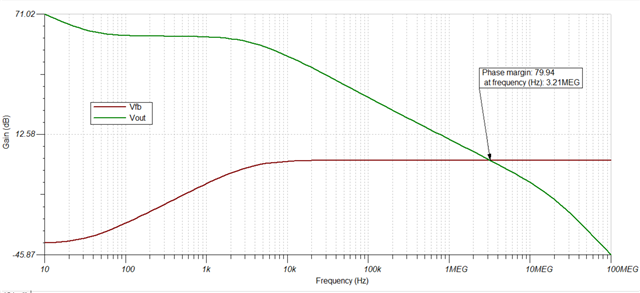

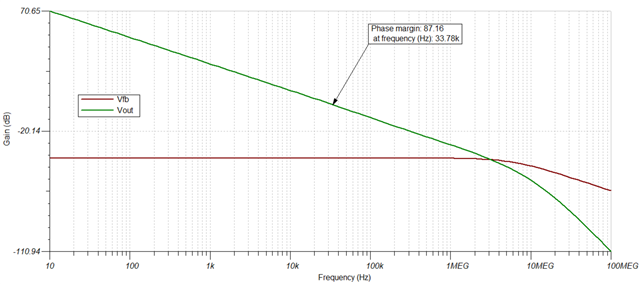

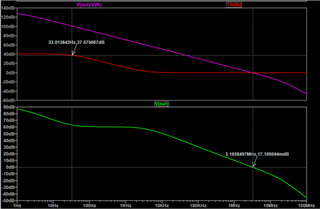

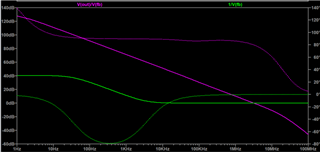

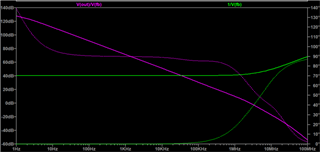

2. I have attached frequency response graphs with and with out feedback capacitor. It is said that to neutralize the affect oh phase due to input capacitors, I am not understanding what are advantages in terms of phase and gain.

3. Does this feedback cap will make RC filter with the feedback capacitor, in this case 33Hz cut off as (10nF and 475k). And is this adding a pole at 33Hz in the feedback loop curve?

4. Also is this the right way to deploy feedback loop break method in case of difference amplifier?

Please help me to understand above queries

Simulation with feedback capacitor

Simulation with out feedback capacitor

Regards,

Sunney