Other Parts Discussed in Thread: , OPA325, THS4551, OPA320, REF5030, THS4561, OPA350, OPA365

Hi,

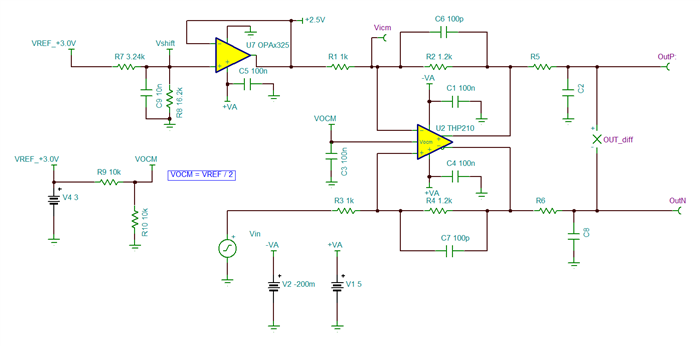

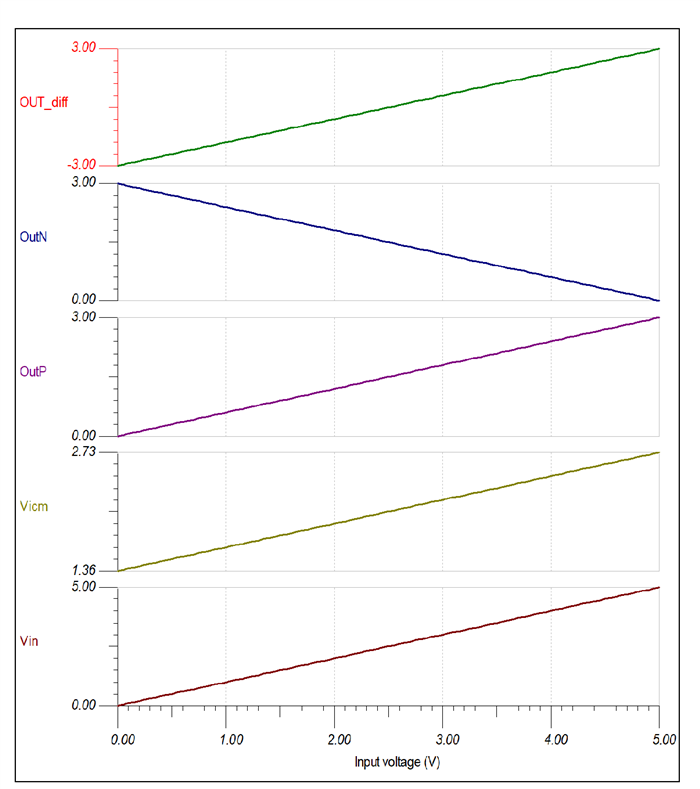

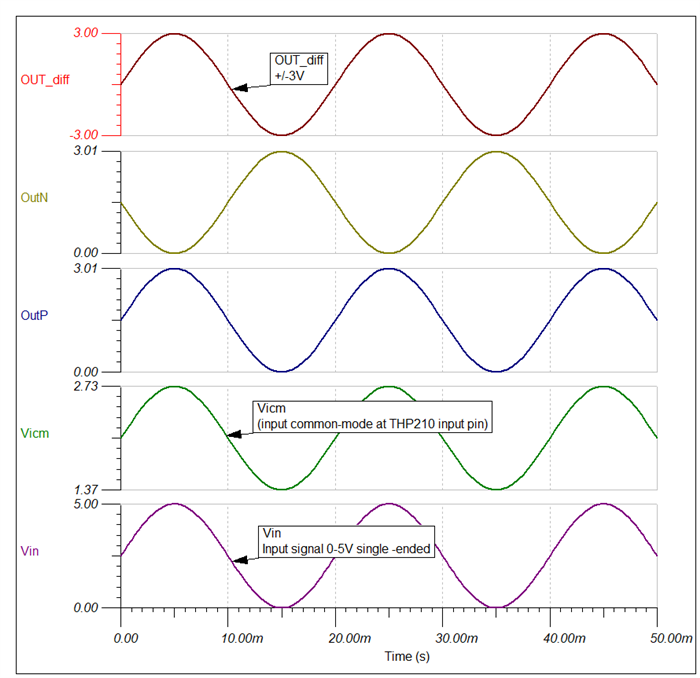

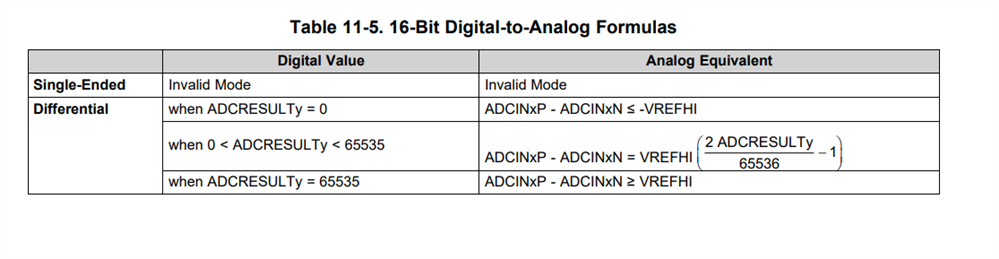

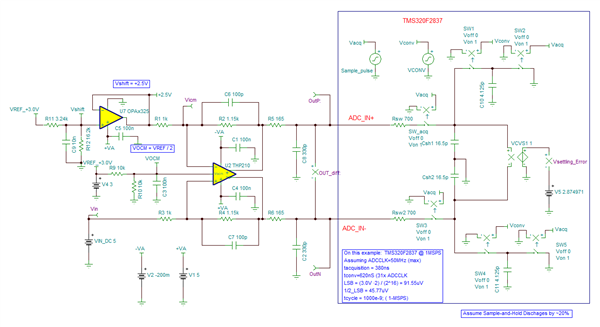

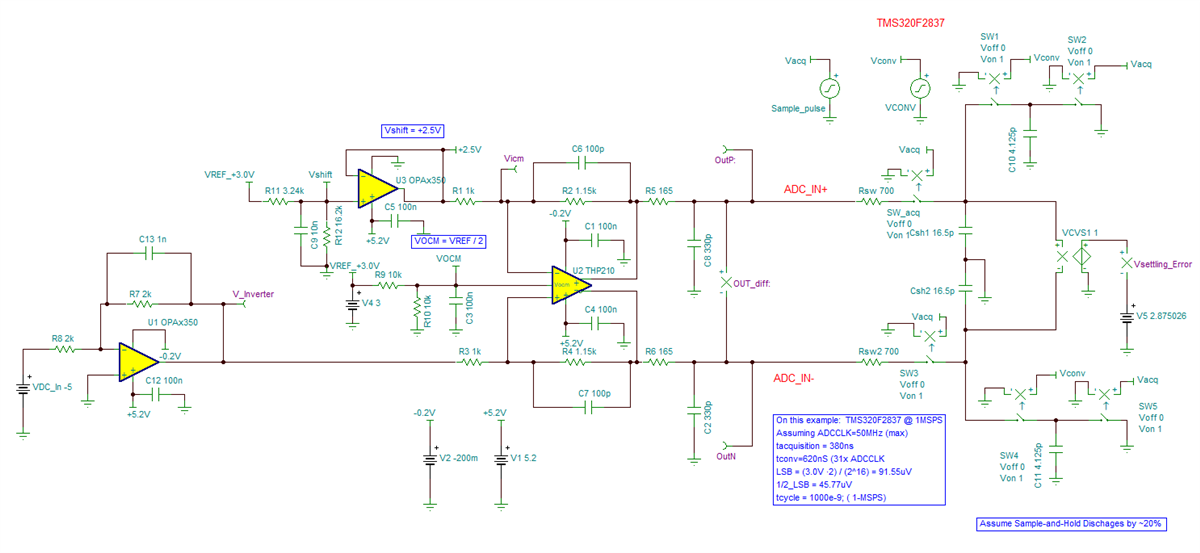

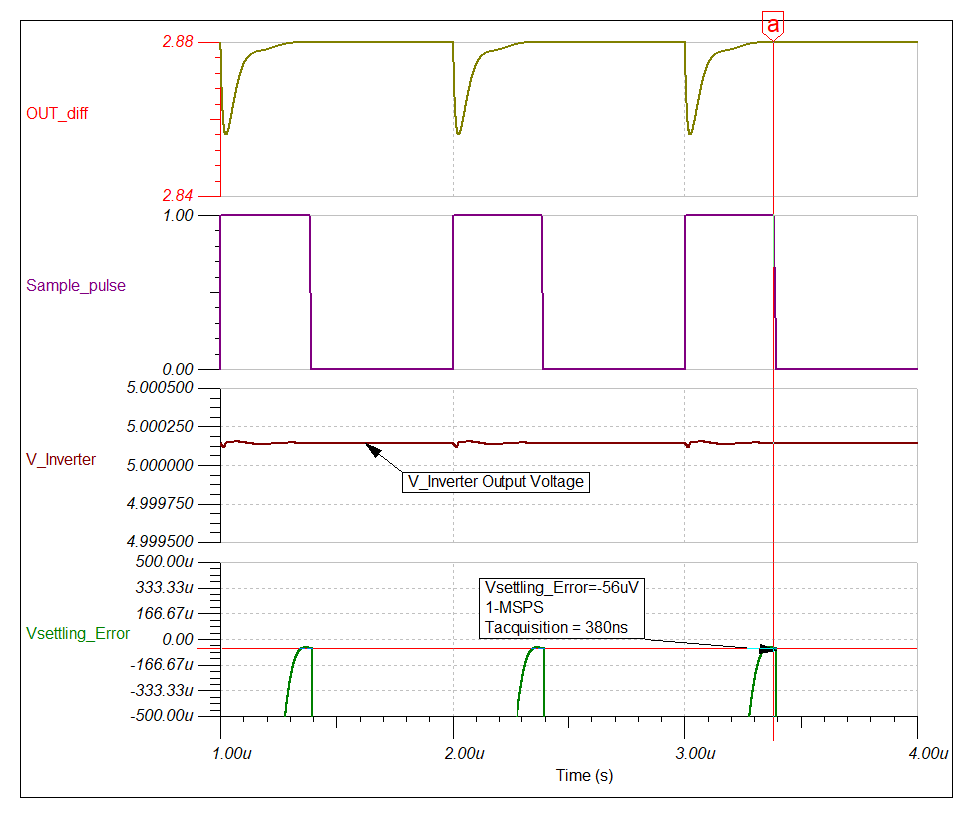

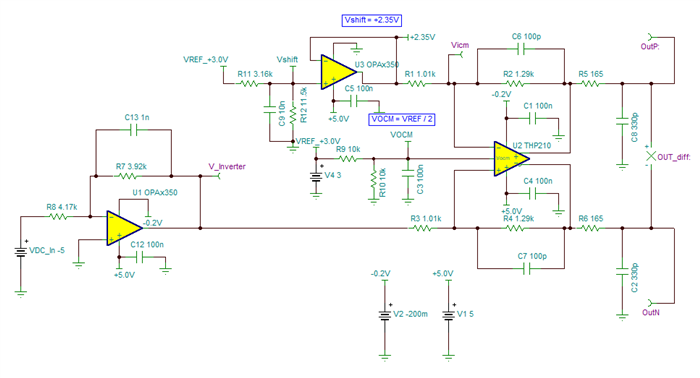

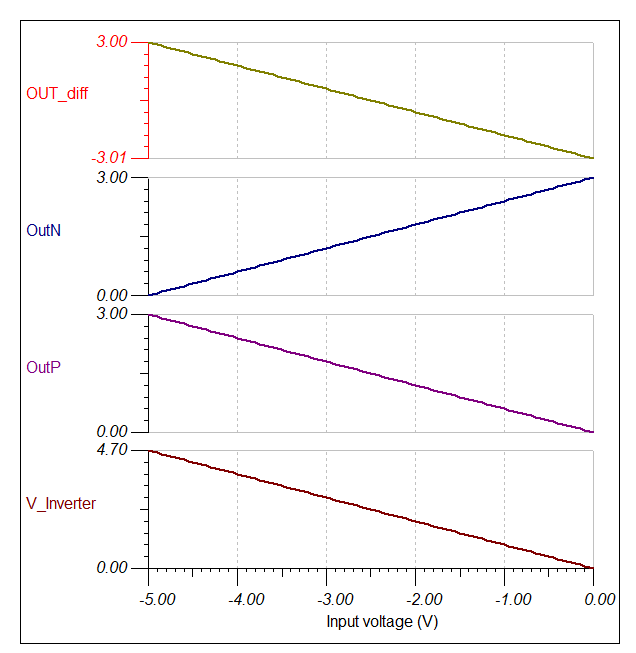

I am looking to use the THP210 to change a single-ended voltage source of 0-5V to a differential representation for measuring by a 16-bit differential ADC.

My question is, should I use the design that is in the EVM for this particular device, or would it be better to follow the more simple designs that are included in the data sheet?

best regards,

Joel